インテル社の新プロセッサ、銅ピラー構造のフリップチップ実装採用:実装技術

プロセッサ・チップとパッケージ基板の接続にCPB技術(CPB:Copper Pillar Bumping)を利用した最初の事例だという。

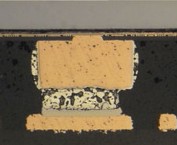

米Intel(インテル)社が2006年1月に発売した、65nm技術で製造したマイクロプロセッサ「Presler」と「Yonah」(いずれも開発コード名)のパッケージ内実装に、従来のPb-Sn(鉛すず)はんだボールに代えて、銅(Cu)ピラー構造のバンプ(CPB:Copper Pillar Bumping)技術を採用していることが明らかになった。解析したのは、カナダのChipworks社である。

同社によれば、この65nmプロセッサは、プロセッサ・チップとパッケージ基板の接続にCPB技術を利用した最初の事例だという。CPB技術は高密度実装が必要なパッケージに向けたフリップチップ実装技術の1つで、従来のはんだバンプに比べると、導電性と熱伝導性に優れ、機械的強度が高く、さらに信頼性を高めることができる。

同社のTechnical Intelligence部門でマネジャーを務めるGary Tomkins氏は、「Intel社の新プロセッサは、65nmルールのSiプロセス技術と歪みSi技術を導入したことだけでも驚嘆に値するが、パッケージ技術でも顕著な飛躍を遂げていたことになる」と述べた。

Chipworks社のシニア・テクノロジ・アドバイザであるDick James氏は、「『Prescott』(開発コード名)など、以前のIntel社製プロセッサは、Pb-Snはんだボールを使った従来のフリップチップ技術を採用していた。それがYonahとPreslerでは、めっき技術で作成したCuピラー構造を使って、チップと基板を接続する方式に変更された。これにより、Pbの使用量を削減できるようになる。最近のPbフリー対応製品の中でも、使用量は少ない部類に入る。当社が知る限り、Intel製プロセッサの中で、CPB技術を採用した最初のプロセッサである」と述べた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 受託開発の内容を「メニュー」としてサービス化、日立が本格展開

- MicrochipがTSMCとの提携を拡大、JASMを通じて40nm特化の生産能力を確保

- 信越化学が国内に新生産拠点、半導体露光材料事業の拡大に向け

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化

- カーボンナノチューブを高効率で合成することに成功、名城大学ら

- TSMCの詳細判明、台湾地震による半導体工場の最新被害/稼働状況

「Presler」に採用されたCuピラー。

「Presler」に採用されたCuピラー。