不揮発メモリ新時代(前編):メモリ/ストレージ技術(3/3 ページ)

電池駆動時間が2倍に伸びる

デジタル機器の利便性も上がる。例えば薄型テレビ受像機はOSを内蔵し、ソフトウェアを多用するため電源切断状態から、全機能が利用できるようになるまで数十秒を要する機種も存在する。ほとんどの製品ではわずかな電力を常に消費して、待機状態を取る。不揮発メモリを使えば、各種デジタル機器が電源投入と同時に利用できるようになり、電源切断手順も単純になる。

システムLSIに次世代不揮発メモリを採用するもう1つの利点は、設計の自由度が増すからだ。例えば、現在のマイコンには、複数のメモリ素子が集積されている。高速なワークメモリにSRAM、不揮発で高速に書き換えでき、プログラムのROM内実行も可能なNOR型、ストレージメモリとしてNAND型、フォントなど書き換えを要しない用途にマスクROMである。それぞれの容量はLSI設計時に固定される。これらを全て1種類の次世代不揮発メモリで置き換えれば、システムLSIを用いる機器メーカーにとって、各用途のメモリ容量を自由に配分できるというメリットがある。

ただし、システムLSIメーカーごとに想定する用途が違うため、採用するメモリの種類も異なる。例えばロームはプロセッサの不揮発化をまず実現するため、素子の分極を利用するFeRAM(Ferroelectric RAM)を選んだ。NECはSRAMの置換も狙うため、高速アクセスとほぼ無制限(1015回)の書き換え回数が実現できるMRAMを用いる。ニューモニクスは現在NOR型フラッシュメモリを中心に携帯電話機での実績があるため、NOR型と似た使い方ができるPRAMを選んだ。

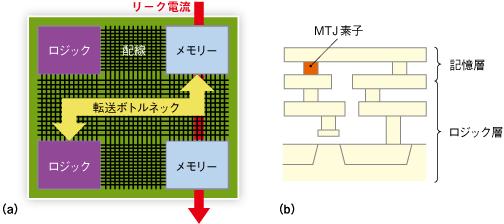

さらに異なる原理に基づく開発を進める動きもある。現在のLSIではロジック回路とメモリ回路は別々のチップにするか、同じチップに配置する場合でも異なる製造プロセスを用いる。東北大学電気通信研究所では、この2つの要素を1つの回路に合わせ込むロジックインメモリ・アーキテクチャを、不揮発メモリを用いて実現しようとしている(図4)†1)。既存のEDAツールなどが一切利用できないため、特定の用途を実現する回路ブロックを設計する手法自体を作り上げる必要があるが、「既存の回路の集積化や処理性能向上の限界を乗り越える手法になり得る。まず、CMOSで設計した論理回路の直上に記憶回路を設計できるため、配置面積が減る。次にメモリ回路の値を検出する電流をそのまま使って演算ができるため、トランジスタ数が減る。つまり省電力だけでなく、集積化にも役立つ」(同研究所ナノ・スピン実験施設の施設長を務める大野英男氏)。

図4 メモリ・イン・ロジックの概念 (a)現在の集積回路ではロジック(演算器)とメモリが分離しているため、動的消費電力が大きく、遅延が生じ、面積が大きくなる。メモリに常時通電しているため、リーク電流も発生する。(b)ロジック層の上部に、MRAMにも用いるMTJ素子を記憶層として配置することで、これらの欠点を解消する。

図4 メモリ・イン・ロジックの概念 (a)現在の集積回路ではロジック(演算器)とメモリが分離しているため、動的消費電力が大きく、遅延が生じ、面積が大きくなる。メモリに常時通電しているため、リーク電流も発生する。(b)ロジック層の上部に、MRAMにも用いるMTJ素子を記憶層として配置することで、これらの欠点を解消する。後編では、PRAMやMRAM、ReRAMなど各種の不揮発メモリの技術開発動向を紹介する。

†1) 畑陽一郎、「磁気トンネル接合素子を使い回路を不揮発化、演算・記憶機能を一体に」、EE Times Japan、2008年10月号、no. 40, pp.22-23.

- Type-C対応デュアルUSBメモリ、サンディスクが7月から出荷開始

- HyperBus対応「HyperRAM」、ボード設計を簡素化しシステム性能を向上

- 「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

- NANDフラッシュ、売価下落も市場規模は拡大――2014年10〜12月

- 平均レスポンスタイム1ms以下、ネットアップのオールフラッシュアレイ

- 磁気メモリの新材料が登場か――ビスマスフェライトで新方向の電気分極を発見

- 高速書き込み/読み出しと優れた耐久性を実現、UHS-I U3対応microSDカード

- 16×20mmサイズ、256GB容量のPCIe対応SSD

- スパンションがMLC NANDメモリに参入――eMMCを製品化

- BDで1ラック当たり1ペタバイトを実現、HLDSの光ディスクライブラリ

関連記事

HPとHynix、メモリスタを2013年に商品化へ

HPとHynix、メモリスタを2013年に商品化へ

抵抗、コンデンサ、インダクタに続く“第4の回路素子”と呼ばれるメモリスタが、2013年にも商品化される見込みである。フラッシュメモリの置き換えを狙うが、ビット当たりの価格をいかに下げるかが今後の課題となりそうだ。 目指すは待機電力ゼロの夢のLSI、東北大が磁性素子利用の不揮発ロジックを実証

目指すは待機電力ゼロの夢のLSI、東北大が磁性素子利用の不揮発ロジックを実証

もはや、従来技術の延長ではこれ以上の消費電力の削減は見込めない。今まさに、半導体チップの基本デバイスの根本的な変革が必要な時期を迎えている。 もうコンセプトだけとは言わせない! 待機電力ゼロの不揮発システムLSIへ前進

もうコンセプトだけとは言わせない! 待機電力ゼロの不揮発システムLSIへ前進

東北大学とNECの研究グループは、スピントロニクス回路を採用した待機電力ゼロの不揮発システムLSIの開発を進めてきた。今回、「不揮発、高性能」、「高集積、低電圧動作」、「高信頼性、高耐久性」という技術要件を満たすべく、5つの要素技術を開発した。 SSDをワイヤレス/バッテリフリーに、東大と慶応大が新技術で狙う

SSDをワイヤレス/バッテリフリーに、東大と慶応大が新技術で狙う

両大学の研究者からなるグループは今回、新たに3つの技術を開発した。フラッシュメモリの寿命を延ばす技術、CPUと高速で接続する技術、大きな電力を高い応答でワイヤレス給電する技術である。これらを統合すれば、128Gビットを超える大容量のワイヤレスSSDを実現できるという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速