8コア内蔵で128GFLOPSを実現、富士通が新SPARCプロセッサを開発:プロセッサ/マイコン

現在最も高速な米Intelのマイクロプロセッサと比較して演算速度は2.5倍に達するという。スーパーコンピュータなどのHPCに向けたプロセセッサである。8コアを内蔵し、各コアは、4つの浮動小数点演算を1度に実行できるSIMD演算命令を備え、1サイクルで2つのSIMD命令を同時に実行できる。

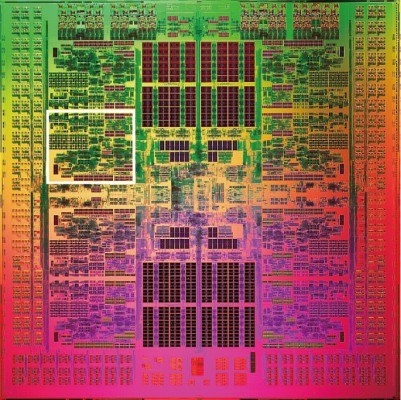

富士通は、プロセッサ単体での浮動小数点演算処理性能が最も高いと主張する「SPARC64 VIIIfx」を開発し、2009年5月14~15日に東京で開催された「富士通フォーラム2009」で試作品を公開した(図1)。

SPARC64 VIIIfxは、環境シミュレーションや航空宇宙など大規模な科学技術計算能力が要求されるHPC(High Performance Computing)に向けたプロセッサ。ピーク演算性能は128GFLOPSに達し、「現在最も高速な米Intelのマイクロプロセッサと比較して演算速度は2.5倍に達する」(同社の説明員)。

2008年に出荷を開始した前世代品に当たる「SPARC 64 VII」は65nmの製造技術を適用し、1つのダイに4個のコアを集積している。新たに開発したSPARC 64 VIIIfxは製造プロセスを45nmに微細化し、コア数を8個に増やした結果、浮動小数点演算性能をSPARC 64 VIIの3倍に高めることができたという(図2)。一方、プロセッサの消費電力をSPARC64 VII(135W)の約1/3に低減できたという。

図1 SPARC64 VIIIfxのウエハー 45nmの製造技術を用いて形成した。ダイの寸法は約2cm角である。左上はプロセッサのパッケージ。この他、SPARC64 VIIIfx 4個と主記憶、冷却装置を実装したシステムボードも展示した。

図1 SPARC64 VIIIfxのウエハー 45nmの製造技術を用いて形成した。ダイの寸法は約2cm角である。左上はプロセッサのパッケージ。この他、SPARC64 VIIIfx 4個と主記憶、冷却装置を実装したシステムボードも展示した。SPARC64 VIIIfxの各コアは、4つの浮動小数点演算を1度に実行できるSIMD(Single Instruction Multiple Data)演算命令を備え、1サイクルで2つのSIMD命令を同時に実行できる。すなわち1サイクルで最大8つの倍精度浮動小数点演算を同時実行できる。

図2 SPARC64 VIIIfxのコア 上下に黒く写っている部分は命令・データ共用の二次キャシュメモリ(合計5Mバイト)。その左右にコアが4個ずつ縦に並ぶ(そのうち1つを白わくで示した)。メモリコントローラーも配置されている。

図2 SPARC64 VIIIfxのコア 上下に黒く写っている部分は命令・データ共用の二次キャシュメモリ(合計5Mバイト)。その左右にコアが4個ずつ縦に並ぶ(そのうち1つを白わくで示した)。メモリコントローラーも配置されている。同プロセッサにはSPARC V9アーキテクチャをHPC向けに拡張したHPC-ACE拡張*1)が施されており、64ビットの浮動小数点レジスタを既存品の32本から256本に増やした。これによって、例えば多元連立方程式を解く場合に、レジスタの値をメモリに退避することなく演算できる可能性が高まるという。

*1)SPARCは1985年に米Sun Microsystemsが開発したプロセッサアーキテクチャ。「V7」から「V9」までが順に登場し、1995年に開発された「V9」では64ビット版が登場した。SPARC64 VIIIfxのアーキテクチャも「V9」である。1999年以降は、同社と富士通がプロセッサの共通仕様(JPS1 Commonality)を共同で開発している。JPS1からの拡張内容は、富士通が2009年2月13日に公開した「SPARC64 VIII fx Extensions」に規定されている。

HPC-ACE拡張によって強化した演算器に向けて、積和演算や平方根、最大値選択など7つの新規命令も追加した。

マルチスレッド処理を高速化するハードウェアバリア機構も設けた。複数のコアで同時実行されているスレッド間の同期処理(待ち合わせ処理)を、ハードウェアによって高速化する機能である。

信頼性向上のため、RAS(Reliability Availability Serviceability)機能を実装した。例えばキャッシュメモリ内の命令やデータに対するパリティチェック機能や、ECCまたは2重化による誤り訂正機能を備える。

命令実行ユニットに対する保護機能も備える。例えば、レジスタ内の値や演算結果はパリティチェックが自動的に実行される。命令実行に失敗した場合は、ハードウェアによって自動的に命令が再実行される。

【EE Times Japan 2009年6月号「Building Blocks」、p.17掲載記事】

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 2

- PR -記事ランキング

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- 自律神経から「頑張りすぎ」を可視化、村田製作所

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- 暗い夜道でも120m先の歩行者を検知、キヤノンが新SPADセンサー

- 商用化から40年を迎えたFPGA、次の主戦場はエッジAI

- 「NVIDIAと真逆の取り組みをしよう」 Jim Keller氏

- JDIの液晶の知見、先端半導体パッケージングの中核技術に

- キオクシアのNAND戦略 「BiCS FLASH」はどう進化するのか

- Micronが12層HBM4をサンプル出荷 前世代品比で性能を60%向上