ARM社のデュアルコアCortex-A9、低消費電力版でも性能はAtomを上回る:マイコン/プロセッサ

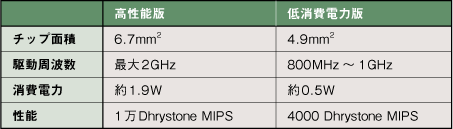

デュアルコアCortex-A9は、2種類のハードマクロの形で提供される。用途に合わせて処理性能を重視した版と、消費電力を重視した版を選択できる。2GHz動作時(1万DMIPS)の消費電力は1.9W、1GHz動作時(4000DMIPS)の消費電力は0.5Wだ。

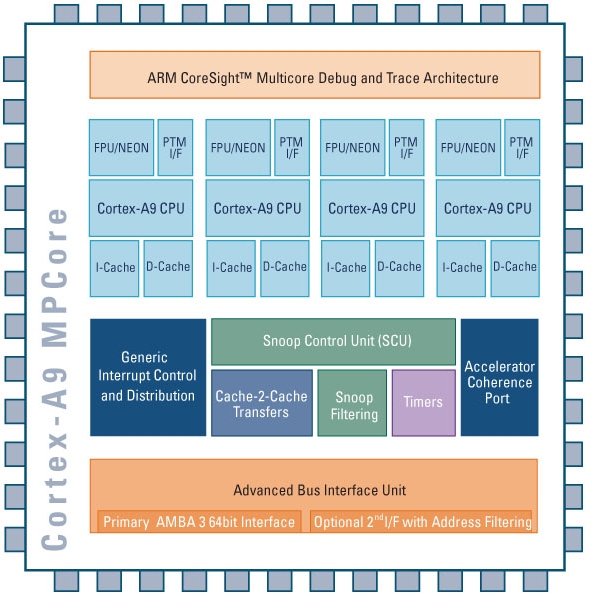

英ARMは、「Cortex-A9 MPCore」プロセッサのデュアルコア版の実装を開発した。「Osprey」と名付けられたこのプロセッサは最大2GHzで動作し、ARMが開発してきたプロセッサの中で最も性能が高い(図1)。

Ospreyは、米Texas Instrumentsの「OMAP-4」に似たものになるようだ。OMAP-4は、2009年秋にサンプル出荷を始める予定のプロセッサで、米Intelの「Atom」プロセッサのシングルコア品と同じチップ面積に2つのCortex-A9コアを集積したものである。

Ospreyは台湾Taiwan Semiconductor Manufacturing Company(TSMC)の40nm汎用(G)製造プロセス技術で製造するハードマクロの形で提供される。少なくともIntelが製造プロセスをさらに微細化するまではAtomキラーとなりそうだ。

ハードマクロには、消費電力と性能の面から最適化された2種類がある(表1)。性能の最適化により、OspreyはARMプロセッサを性能競争という未知の領域に導くことになる。

ARMのプロセッサ部門でマーケティング担当Vice Presidentを務めるEric Schorn氏は、「目標は、一にも二にも性能だ。当社は、ネットブックやスマートブック、携帯型情報機器、テレビ、ホームエンターテインメント機器、さらにはプリンタなどのエンタープライズネットワーク機器といった新市場に参入しようとしている」と述べた。

Schorn氏によれば、Osprey自体はデュアルコアプロセッサだが、ライセンスの提供を受けた企業はさらに多くのコアを集積したチップも作れるという。ARMはまだTSMCから完全なテストチップの提供を待っている段階だ。テストチップは2009年第4四半期に提供される予定である。

ただし、ハードマクロのライセンス供与は既に始まっている。そして、2009年第4四半期にはIP(Intellectual Property)の提供も始まる。2010年中には、ライセンスを取得した企業が独自のSoC(System on Chip)を製造できるようになるはずだ。

性能を追求した実装は、エンタープライズ向けサーバやネットワーク機器、プリンタなどの用途に向けたものだ。チップ面積は6.7mm2で、2GHz動作の場合の処理性能は1万Dhrystone MIPSに達する。消費電力は約1.9Wである。

一方の消費電力低減を重視した実装は、携帯型機器やスマートブック、家電などへの採用を想定している。動作周波数は800MHz~1GHzを超えたあたりになる見込みだ。チップ面積は4.9mm2で、800MHz動作時の処理性能は4000Dhrystone MIPS。消費電力は約0.5Wである。どちらの実装も、製造プロセスとしてTSMCの40nm汎用プロセスを想定している。さらに、リーク電流の少ない40nm低電力プロセスでの製造も可能だ。

Ospreyは、命令とデータに向けた各32Kバイトの1次キャッシュメモリを搭載し、128Kバイト~8Mバイトの二次キャッシュメモリに対応するキャッシュコントローラーを備える。

Atomの性能を上回る

Schorn氏によれば、Ospreyのチップ面積は、45nmプロセス技術で製造するIntelのAtomプロセッサの1/3~1/4の大きさになる。また、ARMは、Embedded Microprocessor Benchmark Consortiumの「Coremark」ベンチマークでOspreyを評価したところ、どちらの実装も1.6GHz動作のAtom N270を上回る性能を発揮したという。消費電力低減を重視した実装では800MHzの動作周波数でAtomの性能を上回り、実行速度について最適化したバージョンでは2GHz動作でAtomの2.5倍の性能を発揮する。

Ospreyの各コアは、画像処理やマルチメディア処理に役立つSIMD命令セット「Neon」向けの演算器や浮動小数点演算器を搭載している。「確かに、ネットワーク機器にNeonや浮動小数点演算器は必要ないかもしれない。しかし、ハードマクロでは、難しい選択に迫られる。Ospreyには、動作実証済みという利点を持たせることが可能だ」(Schorn氏)。

ARMがこのようなハードマクロの形で提供を始めたのは、少し前の「ARM922」や「ARM926」からだ。「ARM926には、構成を変更可能なキャッシュメモリを搭載していた。また、チップメーカーがファウンドリを利用する機会が増え、ファウンドリは低電力向けや汎用、高性能向けというように多様な製造プロセスを提供するようになり、製品化への道筋の選択肢が増えた。見ての通り、現在はハードマクロの数を増加させるようなプロセスの選択肢は減ってきた。当社は、1回の設計で、多くのライセンスを供与したいと考えている」(Schorn氏)。

Scorn氏によれば、Cortex-A9をいち早く導入したARMの顧客である半導体メーカーは、低電力プロセスでプロセッサを実装しているという。「多くのパートナーが低電力プロセスを採用しているので、当社はパートナーのまねをしようとは思わなかった。低電力プロセスが採用されたのは、ワイヤレス機能が関係していたからだ。Ospreyの性能を追求したハードマクロは、Atomと比べて電力効率が4~5倍も高い」。

Ospreyのハードマクロにはグラフィックス機能は入っていないが、興味深いことに、テストチップはこれを搭載している。「Ospreyのテストチップは、グラフィックス機能を提供する『MALI-400グラフィックス処理ユニット』と、動画エンコード/デコード機能を持つ『MALI-VEビデオ・エンジン』を搭載している」(Schorn氏)。

Ospreyは、米Intrinsityの「Fast14」技術も適用されていない。この技術は、韓国Samsung Electronicsが「Cortex-A8」プロセッサの動作周波数を1GHz以上に引き上げるために採用したものだ。「Intrinsityの技術はとてもすばらしい。Cortex-A8への採用実績はあるが、Ospreyで提供しようとするものとは違う。ただし、今後も採用しないというわけではない」(同氏)。

一方、Ospreyは、ARMが他の低電力プロセッサに使っているクロックゲーティング機能を搭載し、低電力設計技法を駆使したものになっている。パイプラインに命令がない場合、主な演算器は電力を消費しない。また、6つの領域に分かれており、それぞれの領域への電力供給を管理することで消費電力を低減する。また、SRAMに命令とデータを保持させたまま、整数演算器パイプラインへの電力供給を切ることも可能だ。これで、スリープ状態から素早く動作を再開させられる。また、キャッシュスヌープ・ユニットと二次キャッシュコントローラー・ユニットは独立して制御される。

Schorn氏は最後に、「このOspreyは、当社がこれまで開発してきたプロセッサとは大きく異なるものだ。OspreyはARMのアーキテクチャの用途を広げることができる。そして、それにはパートナーが欠かせない」と締めくくった。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents 2

- PR -記事ランキング

- 「AppleがSamsungから半導体調達」報道、ソニーの反応は

- 「GaNのコストは5年以内にSi並みに」 ロームの勝ち筋は

- タイワン・セミコンダクターがSiCパワー半導体市場に参入、その狙いは

- 世界半導体製造装置市場、2026年は過去最高に

- アオイ電子がシャープ三重第2工場も買収、先端半導体パッケージ強化

- 「われわれのDNAは製造業」 半導体用材料開発を加速する田中貴金属

- Teslaとの契約はSamsungを回復に導くのか

- 2024年のイメージセンサー市場もソニーがトップ、高まる中国の存在感

- 半導体微細化の立役者! フォトマスクの進化の歴史

- ウエハーの傷にだけ色付けして撮影、検査スピードは数百倍に 東芝

図1 Coretex-A9 MPCoreの機能ブロック 最大で4つのコアを集積でき、Ospreyはデュアルコアである。

図1 Coretex-A9 MPCoreの機能ブロック 最大で4つのコアを集積でき、Ospreyはデュアルコアである。 表1 Ospreyハードマクロの仕様 高性能版と低消費電力版の2種類が用意される。

表1 Ospreyハードマクロの仕様 高性能版と低消費電力版の2種類が用意される。 Windows 8が対応するARM SoCはどれか、3社が勝ち、4社が負ける可能性

Windows 8が対応するARM SoCはどれか、3社が勝ち、4社が負ける可能性 IntelがAtomのロードマップを修正、消費電力でARMに匹敵すると主張

IntelがAtomのロードマップを修正、消費電力でARMに匹敵すると主張 富士通セミコンがARMマイコンを拡充、52品種を追加

富士通セミコンがARMマイコンを拡充、52品種を追加