【ESEC2011】FPGA新興のTabulaがお目見え、「大手のハイエンド品と同等の論理規模で価格は数分の1」:プログラマブルロジック FPGA

ここ数年、FPGAの新興ベンダーが相次いで登場している。SiliconBlue TechnologiesとAchronix Semiconductor、Tabulaで、いずれも米国に本社を置くファブレス半導体ベンダーだ。ESEC2011では、これら新興ベンダーのうちTabulaが日本の展示会に初めて製品を出品した。

米国の新興半導体ベンダーであるTabulaが手掛ける新コンセプトのFPGAが、組み込み機器の総合展示会「第14回組込みシステム開発技術展(ESEC2011、2011年5月11日~13日)」にお目見えした(図1)。半導体の技術商社でTabulaの日本における総代理店を務めるルネサスイーストンが出品した。「Tabulaの製品を日本の展示会に出品するのは今回が初めて」(ルネサスイーストンの説明員)である。

Tabulaは、EDA大手ベンダーのCadence Design SystemsでCTO(最高技術責任者)を務めたSteve Teig氏が2003年に創設した。同氏は配置配線技術の発明者としても知られる。また、現在TabulaのCEO(最高経営責任者)を務めるDennis Segers氏はFPGA大手ベンダーのXilinx出身で、XilinxでハイエンドFPGAファミリ「Virtex」を手掛けた人物である。

図1 高速シリアルの動作を実演 40nm技術で製造するFPGA「ABAX」のうち、既に出荷中の「A1EC04」を搭載した評価ボードを使って、動作を実演して見せた。同FPGAがハードIPの形態で集積している最大6.5Gビット/秒動作の高速シリアルインタフェース(SERDES)の出力をサンプリングオシロスコープに入力し、良好なアイパターンが得られていることをアピールしていた。

図1 高速シリアルの動作を実演 40nm技術で製造するFPGA「ABAX」のうち、既に出荷中の「A1EC04」を搭載した評価ボードを使って、動作を実演して見せた。同FPGAがハードIPの形態で集積している最大6.5Gビット/秒動作の高速シリアルインタフェース(SERDES)の出力をサンプリングオシロスコープに入力し、良好なアイパターンが得られていることをアピールしていた。時分割で回路を切り替えてロジック領域を仮想的に広げる

Tabulaは同社初の製品である「ABAX(エーバックス)」を発表済みで、一部品種については既に出荷を始めている。ABAXの実体はSRAMベースのFPGAであり、その点では大手FPGAベンダーのXilinxやAlteraのFPGAと変わらない。特長は、大手が供給するハイエンドFPGA並みのロジック規模を実現しながらも、価格を大幅に低く抑えられる独自のアーキテクチャを採用していることだ。そのアーキテクチャを「SpaceTime」と呼ぶ。

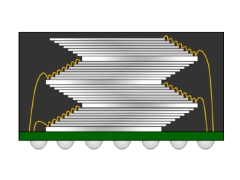

図2 単一のLUTを異なる構成に時分割で書き換えて使う プログラマブルロジック領域に実装した回路を時分割で書き換えることで、同領域の回路規模を仮想的に広げる。物理的な回路規模を抑えてチップ面積を削減し、コストを低減しながらも、実効的なロジック規模を確保する技術である。

図2 単一のLUTを異なる構成に時分割で書き換えて使う プログラマブルロジック領域に実装した回路を時分割で書き換えることで、同領域の回路規模を仮想的に広げる。物理的な回路規模を抑えてチップ面積を削減し、コストを低減しながらも、実効的なロジック規模を確保する技術である。SpaceTimeは、プログラマブルロジック領域に実装した回路をFPGAの動作中に書き換える、いわゆる「動的再構成(ダイナミックリコンフィギュレーション)」技術に基づくアーキテクチャである。ユーザーがFPGAに外部から供給するシステムクロックをFPGAの内部でてい倍して高速のクロック(サブサイクルクロックと呼ぶ)を生成し、その高速クロックでプログラマブルロジック領域を実際に駆動するとともに、リコンフィギュレーションを実行する仕組みだ(図2)。ABAXでは最大8てい倍まで可能で、その際にはシステムクロックの1サイクルで最大8回のリコンフィギュレーションを実行できる。

プログラマブルロジック領域の物理的な規模は一定でも、このように時分割で回路を書き換えることで、実効的なロジック規模を増やせるというわけだ。例えばシステムクロックを8てい倍したサブサイクルクロックで回路を書き換えれば、理論上、実効的なロジック規模を最大8倍まで増やせる計算になる。Tabulaは、チップ上の2次元平面にこうして「時間」の次元を加えることでロジック規模を実効的に増大させたFPGAを、「3PLD(Programmable Logic Device)」と呼ぶ。

サブサイクルクロックごとに書き換える回路のデータは、Tabulaが提供するFPGA開発ツールが自動的に用意する。すなわちユーザーは、「大手ベンダーのFPGAと同じフローでTabulaの3PLDを開発できる。後は開発ツールがユーザーの入力した設計データを解析し、ダイナミックリコンフィギュレーション用の複数の回路データを自動的に生成する。従ってユーザーは、FPGAの内部でダイナミックリコンフィギュレーションが実行されていることを意識する必要がない」(以前にXilinxの日本法人でマーケティング本部長を務め、現在はルネサスイーストンの社外アドバイザーとしてTabulaのマーケティングにかかわるCOMPAS 経営企画室 室長の荒井雅氏)。

大手ベンダーのFPGAも、一部の品種でダイナミックリコンフィギュレーションを利用することは可能だが、使いこなしにかなりのノウハウが求められるため、一般的なユーザーにはハードルが高かった。

チップ面積の削減と歩留まりの向上でコストを大幅に減らせる

この3PLDで価格を大幅に抑えられる理由はこうだ。「大手ベンダーのハイエンドFPGAと同等のロジック規模を実効的に実現しながら、物理的なチップサイズは1/2を下回る大きさに収められる。一般に半導体は、チップサイズが小さくなると製造歩留まりが大幅に改善する。従って、チップサイズが1/2になれば、コストはそれ以上に低減できるわけだ。ABAXは、大手ベンダーのハイエンド品の1/3~1/4といった価格でユーザーに提供できるようになるかもしれない」(荒井氏)。

図3 大手FPGAベンダーのハイエンド品に相当する製品を投入 ルネサスイーストンの社外アドバイザーによれば、TabulaのABAXは大手FPGAベンダーが40nm世代のプロセス技術で製造するハイエンドFPGAに相当するロジック規模を備えているという。ただしこのパネルに記載されているLUT数(Mega LUT)は、物理的な集積規模ではなく、8てい倍のサブサイクルクロックを利用する場合に得られる実効的なロジック規模の最大値である。

図3 大手FPGAベンダーのハイエンド品に相当する製品を投入 ルネサスイーストンの社外アドバイザーによれば、TabulaのABAXは大手FPGAベンダーが40nm世代のプロセス技術で製造するハイエンドFPGAに相当するロジック規模を備えているという。ただしこのパネルに記載されているLUT数(Mega LUT)は、物理的な集積規模ではなく、8てい倍のサブサイクルクロックを利用する場合に得られる実効的なロジック規模の最大値である。ABAXには現在、ロジック規模などが異なる4品種が用意されている(図3)。LUT数は、8てい倍のサブサイクルクロックでリコンフィギュレーションする場合の実効値で「A1EC02」が22万個、「A1EC03」が30万個、「A1EC04」が39万個、「A1EC06」が63万個である。すなわち、LUTの物理的な集積数はこれらの実効値の約1/8にとどまる。既に39万個品のA1EC04の出荷を始めているという。半導体ファウンドリ大手のTSMCが40nm世代のプロセス技術で製造する。

なおABAXでは、ユーザーが外部から供給するシステムクロックは最大800MHzまで対応しているが、FPGA内部でてい倍するサブサイクルクロックは最大1.6GHzまでしか生成できない。そのため、てい倍数はサブサイクルクロックが1.6GHz以下に収まる範囲で利用する必要がある。例えば、外部から供給するシステムクロックが200MHzであれば8てい倍まで利用できる(200MHz×8=1.6GHz)ので8回のリコンフィギュレーションでロジック規模を実効的に最大8倍まで増やせる。一方、システムクロック800MHzのときは2てい倍しか使えない(800MHz×2=1.6GHz)ので、2回のリコンフィギュレーションでロジック規模を実効的に最大2倍までしか増やせない。

採用実績については、海外では通信機器メーカーに採用された実績があるが、「日本では現時点ではまだ実績が無い。これから提案活動を進めていきたい」(ルネサスイーストンの説明員)としている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents 2

- PR -記事ランキング

- 25年2Qの半導体企業ランキング、日本勢トップは13位のソニー

- チップ分解で20年をたどる 「万華鏡」のように変化し続ける半導体業界

- 「ファウンドリー事業完全放棄の可能性」、Intel CEOが言及

- 米国半導体の強化は100%関税よりIntel支援 ── 分社発表から1年、結論を急げ

- GaNパワー半導体市場で拡大狙うサンケン電気、パウデックを吸収合併

- 車載半導体ランキング、首位はInfineonでルネサスは5位

- 「現場ですぐ使えるロボット」普及へ、ソニーが自社コア技術を外部提供

- HBMの代替どころか、勇み足で終わりかねない「HBF」

- トランプ関税は「深刻な自滅行為」、最も得をするのは中国

- 容量5TBで帯域65GB/秒、キオクシアのフラッシュメモリモジュール