アルテラがARMコア搭載FPGAを発表、仮想プロトタイプ環境も用意:プログラマブルロジック FPGA(2/2 ページ)

ハードウェアと開発環境の両軸でザイリンクスと差異化

28nm世代の次世代FPGAにCortex-A9 MPCoreのプロセッササブシステムをハードIPとして集積する――。このコンセプトは、アルテラ最大の競合であるFPGAベンダーのザイリンクス(Xilinx)も「エクステンシブル プロセッシング プラットフォーム(Extensible Processing Platform:EPP)」と呼んで発表しており、既に「Zynq(ジンク)」と名付けた製品の開発ボードを早期採用を検討する顧客に向けて出荷を始めている(参考記事その1、参考記事その2)。

アルテラが今回発表したSoC FPGAも、採用するプロセッササブシステム自体はアーム製であり、ザイリンクスのZynqと変わらない。そこでアルテラは、ハードウェア性能の高さと仮想プロトタイピング環境でザイリンクスとの差異化を図る考えだ。詳しく説明しよう。

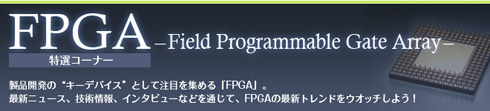

SoC FPGAが訴求するハードウェア性能の高さには、幾つかの要素がある(図6)。第1に、FPGA部とプロセッササブシステムの間をつなぐインターコネクトの帯域幅が広い。Zynqは、インターコネクトの総帯域幅が最大規模品で100Gビット/秒に達する。これに対しSoC FPGAは、Cyclone Vベースの品種で100Gビット/秒以上、Arria Vベースの品種では125Gビット/秒以上が得られると主張する。

第2に、ECC(Error Correcting Code:誤り訂正符号)機能を備えたメモリコントローラをハードIPとして集積している。「競合他社品には無い特徴だ。特に消費者向け機器の分野では、PCを除けばほとんどの機器でECC機能が求められる」(アルテラのHu氏)。

第3に、製造プロセスの選定方針に起因した違いもあるという。アルテラとザイリンクスはいずれも、28nm世代のFPGAの製造を半導体ファウンドリ最大手のTSMCに委託しているが、利用するプロセス技術のオプションは異なる。すなわち、アルテラがハイエンドファミリは「28nm High Performance(HP)」で低コストファミリとミッドレンジファミリは「28nm Low Power(LP)」と使い分けているのに対し、ザイリンクスは28nm世代で用意する全てのファミリに「28nm HPL (High Performance Low Power)」を適用している。これによりアルテラは、「当社のアプローチの方が、応用分野ごとにより最適な特性の品種を供給できる」(Hu氏)と主張する。

図6 ECC付きメモリコントローラや広帯域インターコネクトが特徴 Cyclone Vベースの品種はECC付きメモリコントローラを最大2個集積し、インターコネクトの帯域幅は100Gビット/秒以上。Arria Vベースの品種は同最大4個、125Gビット/秒以上だという。出典:日本アルテラ

図6 ECC付きメモリコントローラや広帯域インターコネクトが特徴 Cyclone Vベースの品種はECC付きメモリコントローラを最大2個集積し、インターコネクトの帯域幅は100Gビット/秒以上。Arria Vベースの品種は同最大4個、125Gビット/秒以上だという。出典:日本アルテラ仮想環境と拡張キットで“FPGAインザループ”の開発フローを提供へ

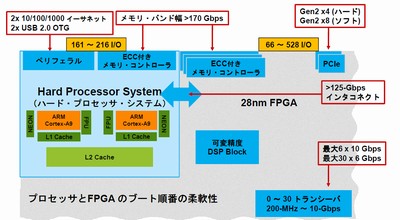

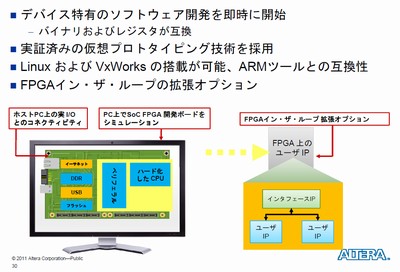

SoC FPGAでアルテラが用意する仮想プロトタイピング環境は、プロセッササブシステムのソフトウェア開発に向けたものだ。「SoC FPGA Virtual Target」と呼ぶ。実体はプロセッササブシステムとSoC FPGAに外付けするメモリチップなど周辺ハードウェアの機能シミュレーションモデルであり、PC上で稼働させることができる(図7、図8)。

このシミュレーションモデルは、プロセッササブシステムのソフトウェアから見ると実機のターゲットボードと同等の機能を備えており、バイナリレベルおよびレジスタレベルの互換性があるという。このモデル上でOSとしてLinuxやVxWorksを動かすこともできる。ARMコアのソフトウェア開発者向けに供給されている各種のツールも利用可能だ。従って、この仮想プロトタイピング環境を使えば、実機が用意できる前に先行してソフトウェア開発を進められる。「このようなソフトウェア開発環境を提供するのは、FPGA業界では初めてだ」(Hu氏)という。EDAツール大手ベンダーのシノプシス(Synopsys)が既に製品として供給し、市場で実績がある仮想プロトタイピングツールをベースにした。

さらにアルテラは今後、この仮想プロトタイピング環境の拡張オプションとして、PCI Expressインタフェース経由でPCにつないで使う開発キットも用意する。これを使えば、SoC FPGAのFPGA部に載せるハードウェアアクセラレータなどのIPコアも、機能シミュレーションモデルとして仮想プロトタイピング環境で利用できるようになるという。HILS(Hardware in the Loop Simulation)になぞらえて「FPGA in the Loop」と呼ばれる手法を適用して、SoC FPGAのソフトウェアを開発することが可能になる。

SoC FPGA Virtual Targetは2011年10月12日から受注を開始し、FPGA in the Loop対応の拡張オプションについては2012年の初期から提供を始める予定だ。いずれも価格は明らかにしていないが、Virtual Targetについては「市場にある既存ツールと同等にする」(Hu氏)という。

図7 仮想プロトタイピング環境を提供 SoC FPGA Virtual Targetの概要である。拡張オプションの開発キットを使えば、FPGA上のユーザーIPも機能モデルとしてこの環境に取り込んで、いわゆる「FPGA in the Loop」の手法でソフトウェアを開発できるようになる。出典:日本アルテラ

図7 仮想プロトタイピング環境を提供 SoC FPGA Virtual Targetの概要である。拡張オプションの開発キットを使えば、FPGA上のユーザーIPも機能モデルとしてこの環境に取り込んで、いわゆる「FPGA in the Loop」の手法でソフトウェアを開発できるようになる。出典:日本アルテラ関連キーワード

FPGA | アルテラ | 28nmプロセス | ザイリンクス | DSP(Digital Signal Processor) | ネットワークカメラ | PCI Express | H.265 | TSMC

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- 信越化学が国内に新生産拠点、半導体露光材料事業の拡大に向け

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 受託開発の内容を「メニュー」としてサービス化、日立が本格展開

- MicrochipがTSMCとの提携を拡大、JASMを通じて40nm特化の生産能力を確保