次世代メモリ「HMC」の仕様バージョン1を公開:メモリ/ストレージ技術

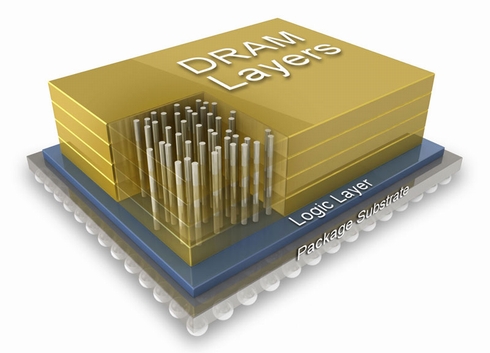

DRAMチップを3次元方向に積層し、シリコン貫通電極で接続するHybrid Memory Cube(HMC)。転送速度が大幅に高速化するHMCが早期に製品化されれば、あらゆる機器に大きな改善をもたらすだろう。

次世代DRAMであるHybrid Memory Cube(HMC)の普及を目指すコンソーシアム「Hybrid Memory Cube Consortium」は2013年4月3日、HMCの「バージョン1」を公開した。同コンソーシアムは、Micron TechnologyやSamsung Electronics、SK Hynixなどが主導するもので、STMicroelectronics、ルネサス エレクトロニクス、富士通、GLOBALFOUNDRIESなど100社以上が参加している。だが、IntelやNVIDIAなどは参加していない。

HMCは、3次元方向に積層した複数のDRAMチップをシリコン貫通電極(TSV)で接続する。

バージョン1では、メモリを実装したときのプロセッサとの距離が8~10インチの「short-reach」と、より近い距離の「ultra short-reach」について、転送速度を定めている。short-reachでは転送速度を最大28Gビット/秒(Gbps)に、ultra short-reachでは15Gbpsに向上することを目指す。バージョン1は、2014年第1四半期に完成する見込みである。

SK HynixのDRAM製品化部門でバイスプレジデントを務めるJH Oh氏は、「HMCはメモリに新たなレベルの性能をもたらした。メモリの性能は飛躍的に高まり、“メモリの定義”を変えることになるだろう」と述べた。

MicronのDRAMマーケティング部門でバイスプレジデントを務めるRobert Feurle氏は、「HMCが実用化されれば、コンピュータシステムはもちろん、最終的には民生用途に抜本的な改善をもたらすと確信している」と語った。

一方、米国の電子部品関連標準化団体 「JEDEC Solid State Technology Association」は、既存のメモリインタフェース「Wide I/O」の後継規格として、高帯域幅のメモリインタフェースの標準化に取り組んでいると言われている。

【翻訳:青山麻由子、編集:EE Times Japan】

- Type-C対応デュアルUSBメモリ、サンディスクが7月から出荷開始

- HyperBus対応「HyperRAM」、ボード設計を簡素化しシステム性能を向上

- 「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

- NANDフラッシュ、売価下落も市場規模は拡大――2014年10~12月

- 平均レスポンスタイム1ms以下、ネットアップのオールフラッシュアレイ

- 磁気メモリの新材料が登場か――ビスマスフェライトで新方向の電気分極を発見

- 高速書き込み/読み出しと優れた耐久性を実現、UHS-I U3対応microSDカード

- 16×20mmサイズ、256GB容量のPCIe対応SSD

- スパンションがMLC NANDメモリに参入――eMMCを製品化

- BDで1ラック当たり1ペタバイトを実現、HLDSの光ディスクライブラリ

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -記事ランキング

- 中国はどうEVバッテリー市場を支配したか 欧米のミスは「固体電池への幻想」

- 「充電5分で520km走行」を巡る疑問、 中国CATLの車載バッテリー発表を考察

- DRAM市場でSK hynixが首位独走、Samsung引き離す 25年Q2

- 米国の中国向け装置輸出「特例撤回」 SamsungとSKへの影響は

- あと5年で中国が半導体生産能力トップに 米国は先端ノード強化

- ロームのSiC搭載インバーター部品が量産開始、中国大手の新型EVに

- 「標準化を待てず」 HBMで変わるメモリ技術サイクル

- NEDOの手を離れ本格ビジネスへ レゾナックが27社参画の「JOINT3」設立

- 「メモリの壁」突破でエッジAIを次の段階に、CEA-LetiとST幹部が語る

- GaNで半導体製造の欠陥検出 キオクシア岩手で検証へ

HMCの構造。メモリコントローラやプロセッサとの通信インタフェースを兼ねる物理層の上に、TSVで接続されたメモリチップが積層されている。

HMCの構造。メモリコントローラやプロセッサとの通信インタフェースを兼ねる物理層の上に、TSVで接続されたメモリチップが積層されている。 スピン注入式の新型MRAMがいよいよ製品化、2015年にはギガビット品が登場へ

スピン注入式の新型MRAMがいよいよ製品化、2015年にはギガビット品が登場へ マイコンの進化を不揮発メモリが助ける、パナソニックが「ReRAM」を採用

マイコンの進化を不揮発メモリが助ける、パナソニックが「ReRAM」を採用 次世代不揮発性メモリ市場が成長、MRAMとPCMは2016年に10億ドル規模へ

次世代不揮発性メモリ市場が成長、MRAMとPCMは2016年に10億ドル規模へ