シリコンコンバージェンスを可能とするアルテラSoC、開発環境も整う:ビジネスニュース 企業動向

FPGAベースの設計手法は、設計の柔軟性を確保しつつ最先端プロセス技術を活用できることから注目を集めている。こうした中で「シリコンコンバージェンス」を提唱しているアルテラは、最先端FPGA技術をベースとしたSoC設計を推進している。

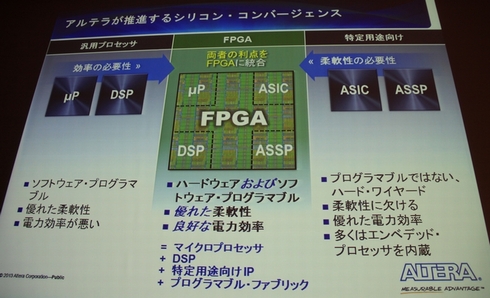

日本アルテラは2013年5月15日、東京都内で「アルテラ SoC シンポジウム」を開催した。同社は先端FPGA技術をベースとして、汎用プロセッサとASIC/ASSPの機能を1チップに統合する「シリコンコンバージェンス」を提唱している。今回のシンポジウムでは、高度なシリコンコンバージェンスを可能とするアルテラの28nm SoC製品とその開発環境を紹介した。

さまざまな電子機器には、システムを制御したり、ある機能を実行、処理したりするために、汎用プロセッサやASIC/ASSPなど複数のICチップが用いられている。一方でICチップは微細プロセス技術の進歩もあり、多くの機能を1チップに集積することが可能となった。特に、SoCを実現するにあたってFPGAベースの設計手法は、設計の柔軟性を確保しつつ最先端プロセス技術を活用できることから注目を集めている。こうした中でアルテラは、最先端FPGA技術をベースとしたSoC設計を推進している。

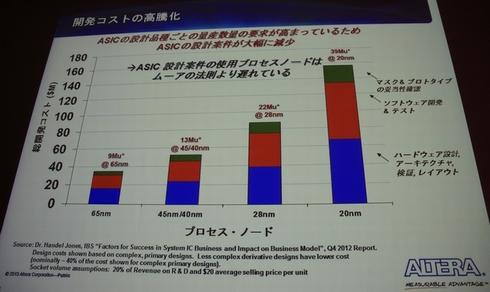

FPGAの需要が拡大している背景にはいくつかの理由があるが、その中でも特筆されるのはASICの設計コストが高騰している点である。日本アルテラの社長を務める日隈寛和氏は、「ASICにおけるプロセスノードごとの総開発コストは、40/45nm世代で50億円以上となり、20nm世代では150億円を超えるとみられている」と話す。つまり、携帯電話やゲーム機器など大量に生産される製品でない限り、ASICの設計手法を用いて、システムレベルの機能を1チップに集積することはコスト的にも難しくなってきた。これに対して、FPGAはこうした課題に対処できるデバイスの1つでもあり、ASICからFPGAへの移行が進むきっかけとなっている。

TOPPERSプロジェクト、マルチプロセッサ向けRTOSなどを2013年度中にサポート

日隈氏に続いて、名古屋大学 大学院情報科学研究科 附属組込みシステム研究センター(NCES)の准教授を務める本田晋也氏が、「プロセッサ内蔵FPGA(アルテラSoC)への期待とソフトウェアプラットフォーム」というテーマで基調講演を行った。

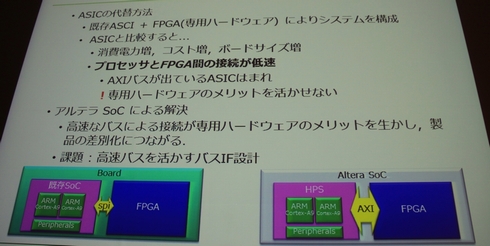

本田氏はまず、組込みシステム開発の現状に触れた。組込みシステムを設計するには、開発済みのSoCとFPGAをボード上で組み合わせてシステムを構成する方法がある。しかし、この方法ではプロセッサとFPGA間を接続するバスの速度が遅くなり、設計通りのシステム性能が得られないことがある。また、予想以上に消費電力が増えたり、コストが増加したりすることもある。これに対して、「アルテラSoCを用いると、HPS(Hard Processor System)とFPGA間を高速のAXIバスで接続することができ、ボード上で生じていたバス速度のボトルネックを解決することができる」と本田氏は述べた。

ボード上でシステムを構成する場合は、プロセッサとFPGA間のバス速度がボトルネックになることもある。アルテラSoCではHPSとFPGA間を高速のAXIバスで接続することができるため、ボトルネックを解消することができる (クリックで拡大) 出典:NCES

ボード上でシステムを構成する場合は、プロセッサとFPGA間のバス速度がボトルネックになることもある。アルテラSoCではHPSとFPGA間を高速のAXIバスで接続することができるため、ボトルネックを解消することができる (クリックで拡大) 出典:NCESアルテラSoCには、HPSに「ARM Cortex-A9 MPCore」が内蔵されている。本田氏は、「Cortex-A9は多くの用途で利用されており、他のARMコア同様に、市場で長期間使われ、開発したソフトウェア資産を有効に活用できる可能性が高い。その上、OSやコンパイラ、開発環境など、すでに市場で流通しているソフトウェアエコシステムを利用できることもメリットだ」と述べる。その一例として、アルテラ製品の販売代理店であるアルティマなどから安価に提供されているアルテラSoCの評価ボードなどを挙げた。アルテラSoCが、ヘテロジニアスなマルチプロセッサアーキテクチャの研究開発に有用なプラットフォームであることも付け加えた。

さらに本田氏は、アルテラSoCの設計フローと、設計ツールについて紹介した。実際の設計ではシステム仕様に基づいて「アーキテクチャ」、「ソフトウェア」、「ハードウェア」、「インタフェース」などを開発することになる。これらの開発を支援するツールとして、「アーキテクチャの自動決定ツール」、「システムレベル設計ツール」、「ソフトウェア開発ツール」、「ハードウェア開発ツール」、および各種の「デバッグ/検証ツール」などを紹介し、それぞれの機能や特長、活用時の注意点などについて解説した。

最後に本田氏は、アルテラSoCに関連した、TOPPERSプロジェクト/NCESの取り組みについて述べた。現状でアルテラSoCをサポートする製品はないが、「2013年度中にはアルテラSoCに対応したマルチプロセッサ向けRTOS『TOPPERS/FMPカーネル』、組込みシステム向けに仮想化をサポートするデュアルOSモニタ『SafeG』、およびシステムレベル設計環境『SystemBuilder』を順次サポートしていく予定である」と語った。

シリコンコンバージェンスを実現するアルテラSoCと開発環境

日本アルテラでマーケティング部長を務める堀内伸郎氏は「アルテラの組込み機器向け製品とソリューションの概要」と題して講演した。冒頭、堀内氏は組込みプロセッサ市場におけるアルテラの歩みなどを紹介。「1984年に世界初のPLDを開発し、それ以降はPLD/FPGA業界を常にリードしてきた」と語る。その1つが2000年に発表した、プロセッサ内蔵の「Excalibur」である。ハードコアの「ARM9」プロセッサなどを搭載したFPGAである。当時は180nmプロセスで製造され、FPGAに内蔵された「ARM922T」プロセッサコアの動作周波数は最大200MHzであった。「一般的なASIC/ASSPに用いられる製造プロセスは、FPGAより2世代程度先行していた。このため性能や消費電力、チップコストなどの点でASIC/ASSPには及ばず、Excaliburは研究開発などに用途が限られるなど、広く普及するまでには至らなかった」(堀内氏)と振り返る。

こうした中でアルテラは現在、ARM Cortex-A9 MPCoreをハードコアで実装した28nmプロセスで製造するSoC(Cyclone V/Arria V)を供給している。HPSとFPGA間のバス幅は最大125Gビット/秒の帯域幅があり高速インタコネクトを実現する。さらに、FPGA向けソフトコアプロセッサとして、「Nios II」をはじめ、「ColdFire V1」や「Cortex-M1」、「MP32」を提供するなど、用途に応じて選択できるプロセッサアーキテクチャと実装環境を用意した。

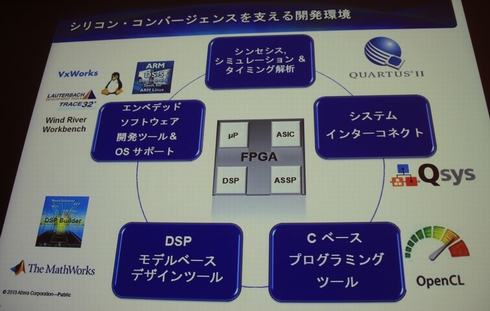

日本アルテラは、シリコンコンバージェンスを支える開発環境も整えた。FPGA開発ツールの「QUARTUS II」をはじめ、システムレベル統合ツールの「Qsys」、並列コンピューティングのフレームワーク「OpenCL」、DSP設計ツール「DSP Builder」、および組込みソフトウェア開発環境/OSとして「VxWorks」や「ARM DS-5」などが利用できる。

さらに、Linuxコミュニティポータルとして、「Rocket Boards.org」を立ち上げた。堀内氏によれば、「アルテラSoCユーザーが参加できるオープンソースコミュニティで、Linuxソースコードや資料、開発ツールなどを配布するなど、Linuxリソースセンター的な役割も担っている」という。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- 自動運転のキーデバイスとなる車載SoC

- キオクシアが攻める「NANDとDRAMのあいだ」 NVIDIAと協業も

- 次はデータセンター 「スマホ以外」にも手を広げるQualcomm

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- 村田製作所、マイクロ一次電池事業をマクセルに譲渡

- AMDがAI新興Untether AIのエンジニアチーム「だけ」買収

日本アルテラの社長を務める日隈寛和氏

日本アルテラの社長を務める日隈寛和氏

名古屋大学 大学院情報科学研究科 附属組込みシステム研究センターの准教授を務める本田晋也氏

名古屋大学 大学院情報科学研究科 附属組込みシステム研究センターの准教授を務める本田晋也氏 日本アルテラでマーケティング部長を務める堀内伸郎氏

日本アルテラでマーケティング部長を務める堀内伸郎氏

アルテラが車載分野への本格展開を宣言、年率20%以上の売上高成長を見込む

アルテラが車載分野への本格展開を宣言、年率20%以上の売上高成長を見込む アルテラがARMコア搭載FPGAを発表、仮想プロトタイプ環境も用意

アルテラがARMコア搭載FPGAを発表、仮想プロトタイプ環境も用意 “シリコンコンバージェンス”へ、3次元FPGAの取り組みをAlteraが説明

“シリコンコンバージェンス”へ、3次元FPGAの取り組みをAlteraが説明