ルネサス、コストかけずに高速I/O搭載LSIを実現する設計技術開発:プロセス技術(1/2 ページ)

ルネサス エレクトロニクスは、LSIと実装基板の間に生まれるインピーダンス差による信号劣化をパッケージ基板内に存在する寄生容量をコントロールして抑える技術として、25Gビット/秒の高速なデータ伝送にも対応する手法を開発した。既に新技術を適用したASICの設計を進め、早ければ2014年にも新技術を搭載したLSIの生産を実施する。

電気的特性値を示すインピーダンスは、LSIやプリント基板などの構造や寸法、周波数依存性などによって決まる。信号伝送回路では、送り手と受け手のインピーダンスが整合されている(インピーダンスに差がない)場合に、受け手が受け取る電気信号が最大になる。逆に、インピーダンスに差がある不整合の状態では、信号の反射が発生するため、受け手の受ける電気信号のエネルギーは弱くなる。さらに、不整合が大きくなれば、電気信号が配線間で反射を繰り返すという現象が起こる。正しい信号波形に多くの反射波が合わさることで波形が乱れ、信号品質が劣化してしまう。

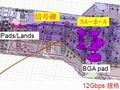

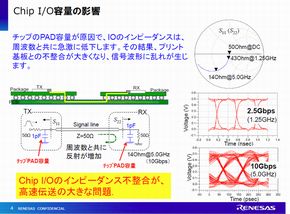

LSIは、チップやパッケージの端子部分などに容量(寄生容量)を持つため、LSIがより高い周波数信号を扱うことでインピーダンスが低下し、LSIを実装する実装基板との間のインピーダンス不整合が大きくなる傾向にある。そのため、高周波信号を扱うLSIは、実装基板とのインピーダンス不整合を整合する仕組みが必要になった。

最も一般的な整合方法は、チップにインダクタを用いた整合回路を構成する手法がある。しかし、コストと比例するチップサイズの拡大を招くという課題を抱える。

チップサイズを増大させない整合回路として、チップを搭載するパッケージ基板にコイルなど受動部品を埋め込み整合回路を形成する方法も検討されているが、現時点では、本格的な実用化には至っていない。

信号劣化を、パッケージ基板設計で抑える技術

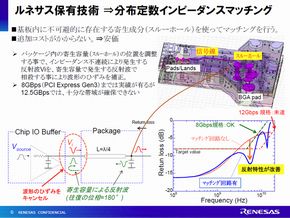

そこでルネサスでは、製造コストを抑えながら、低インピーダンスのLSIでも、より高周波信号を扱える技術を独自に開発し、2008年頃から各種LSIに適用してきた。

このルネサスの技術は、インピーダンスの整合を行わずに、インピーダンスの不整合に伴う信号劣化を、パッケージ基板設計で抑えるという技術だ。必要なのは「設計の工夫」だけで、特殊な製造技術や回路を要さず、コストの増大を招かないという特徴を持つ。

信号劣化を抑える仕組みは、信号劣化を招くインピーダンス不整合による反射波に対し、逆位相波を与え、相殺するというもの。逆位相波は、パッケージ基板のスルーホールや配線が持つ寄生容量を使って生成させる。具体的には、スルーホールの寄生容量で打ち消したい反射波の1/4波長(90°位相、往復位相が180°になる)の反射波を発生させるように位置を調整して配置することで、信号劣化の抑制を実現する。ルネサスでは、この技術を「分布定数インピーダンスマッチング」と呼んでいる。

ルネサスでは、これまで最大転送レート5Gビット/秒のUSB3.0や同8Gビット/秒のPCI Express Gen3規格に対応したLSIなどに適用してきた。しかし、「分布定数インピーダンスマッチング技術は10Gビット/秒程度の対応が限界で、10Gビット/秒以上の高速信号転送に対応するには、新たな技術開発が必要になった」(ルネサス)とする。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速