富士通研究所、従来比3倍の3000原子規模ナノデバイスのシミュレーションに成功:新技術

富士通研究所は、ナノデバイスの電気特性をシミュレーションする技術として従来比3倍となる3000原子規模のナノデバイスに対応する技術を開発したと発表した。この技術により、新材料を用いるなどした次世代デバイスの開発期間/コストを削減できるという。

富士通研究所は2014年1月14日、3000個程度の原子で構成される規模のナノデバイスの電気特性をシミュレーションする技術を開発したと発表した。スパコンを用いた大規模並列化技術と計算に利用するメモリ容量を削減する技術などで、従来よりも3倍となる3000原子規模の電気特性シミュレーションを可能にしたという。この技術により、新材料を用いるなどしたナノデバイスを試作する前に、より正確に電気特性を把握できる。

システムLSIなどナノデバイスは、微細化がより技術的に難しくなり、新しい材料や新しい構造を用いた次世代デバイス開発が活発に行われている。ただ、次世代デバイスの開発は、電気特性を測定、評価するために試作実験を繰り返す必要があり開発期間/コストの増大を招いた。一方で、新型デバイスの電気特性を計算機上で正確にシミュレーションできれば、試作実験を行う回数を大幅に減らすことが可能になり、開発期間/コストの削減が期待できる。

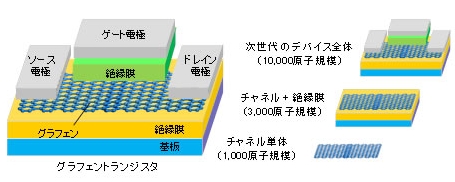

ナノデバイスの電気特性を正確にシミュレーションするには、1つ1つの原子の振る舞いを正確に計算する「第一原理計算」によるシミュレーションが有効とされている。しかし第一原理計算は、膨大な計算が必要なため、電気特性予測に適用する場合、「1000原子規模にとどまっていた」(富士通研究所)。そのため、シミュレーションできる規模も「電子の通り道であるチャネル部分だけの計算が可能であり、電気特性に大きな影響を及ぼすと考えられる隣接する電極や絶縁膜との相互作用を取り入れるのに必要な原子、数千個規模のシミュレーションを実現することができなかった」という。

そこで富士通研究所では、より大規模な構造でも第一原理計算による電気特性予測を可能にする技術の開発を実施。今回、計算精度を保ちながら計算に利用するメモリ量を削減する計算手法と、スパコンの活用により、従来比3倍となる3000原子規模に対応する電気特性シミュレーション技術を開発した。

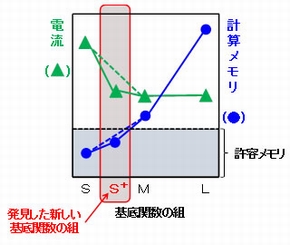

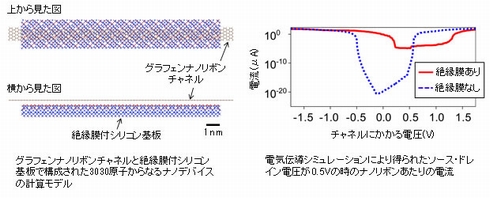

電気特性シミュレーションでは、電気の流れを表すために基底関数の組を用いる。通常、基底関数の数が増えると計算結果の得られる電流値は正しい値に近づいていくが、一方で使用する計算メモリ量が増加してしまう。今回、富士通研究所では計算精度を保持しながら、計算メモリを約1/4、計算時間を約1/25に削減できる基底関数の組を発見したとする。「基底関数の組の発見により、利用メモリを汎用スパコンの許容メモリ以下にすることができ、3000原子規模のナノデバイスの電気特性を約20時間で予測することが可能になった」という。富士通研究所では、今回の技術を用いて、グラフェンと絶縁膜で構成された3030原子からなるナノデバイスの電気特性のシミュレーションを実施するなどしている。

今後の技術開発などについて富士通研究所では、「計算機の性能向上に足並みを合わせたさらなる大規模並列化技術の開発により、より大規模で効率的な計算を追求し、数年中にナノデバイス全体のシミュレーションを達成すること(1万原子規模)で、計算機上でのナノデバイス設計の実現を目指す」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -- EE Times Japanテ勇DN Japan 邨ア蜷磯崕蟄千沿�� 蜊雁ー惹ス捺・ュ逡� 縺薙l縺セ縺ァ縺ョ20蟷エ縲√%繧後°繧峨�20蟷エ窶補� 髮サ蟄千沿2025蟷エ6譛亥捷

- 繧「繝励Μ繧ア繝シ繧キ繝ァ繝ウ縺ョ隕∽サカ縺ォ蠢懊§縲√す繧ー繝翫Ν繝√ぉ繝シ繝ウ縺ョ豸郁イサ髮サ蜉帙r蜑頑ク帙☆繧区婿豕�

- 菴取カ郁イサ髮サ蜉幢シ城ォ倡イセ蠎ヲ縺ョ繧キ繧ー繝翫Ν繝√ぉ繝シ繝ウ縲∵ウィ諢上r謇輔≧縺ケ縺阪ち繧、繝溘Φ繧ー隕∝屏縺ィ縺ッ��

- 譛ャ迚ゥ縺ィ隕句�縺代′縺、縺九↑縺�キァ螯吶↑蛛ス騾�蜊雁ー惹ス楢」ス蜩√∽シ∵・ュ縺瑚ェソ驕斐〒豌励r莉倥¢繧九%縺ィ縺ッ��

- Intel縲∽サ翫←縺�↑縺」縺ヲ繧具シ溘闍ヲ蠅�r謚懊¢蜃コ縺帙k縺�

Special Contents 1

- PR -記事ランキング

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- センサーで微細プロセス、ロジックも12nm導入へ ソニーのイメージセンサー戦略

- ルネサスがWolfspeedの再建支援、Q2には2500億円の減損か

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- AMDがAI新興Untether AIのエンジニアチーム「だけ」買収

- ロームとNVIDIA、AIファクトリー実現に向け協業

- 自動運転のキーデバイスとなる車載SoC

- TELとimecが「戦略的パートナーシップ」を5年延長

- 全固体電池向けの固体電解質市場、2030年以降に急加速か

次世代デバイスの一例とその原子規模例 出典:富士通研究所

次世代デバイスの一例とその原子規模例 出典:富士通研究所 今回、富士通研究所が発見した新しい基底関数の組の効果を示す図 出典:富士通研究所

今回、富士通研究所が発見した新しい基底関数の組の効果を示す図 出典:富士通研究所

スパコン「京」で重レアアースレス磁石開発を加速!

スパコン「京」で重レアアースレス磁石開発を加速! 「高周波シミュレータがあれば設計できる?それは錯覚」、アイラボ市川氏が語る

「高周波シミュレータがあれば設計できる?それは錯覚」、アイラボ市川氏が語る 富士通研、書籍を裁断せずに歪みなく電子化する技術

富士通研、書籍を裁断せずに歪みなく電子化する技術