ザイリンクスが400Gb イーサネットの動作デモを公開――20nmFPGAで:プログラマブルロジック(2/2 ページ)

32.75Gb/sトランシーバ×16チャネル

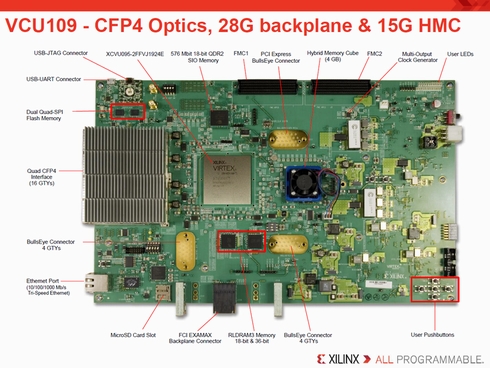

披露したデモボードは、GTYを32個搭載するXCVU095とともに、CFP4仕様の100Gビット/秒 光トランシーバ/光デバイス(CFP4 光インタフェース)が4個や次世代DRAMであるHybrid Memory Cube(HMC:容量4Gバイト)、バックプレーン接続用コネクタなどを搭載し、通信機器などへの応用を見越した構成だ。

CFP4 光インタフェースとの接続は、GTYを4×4個(計16チャネル)を使用し400Gビット以上の帯域幅を確保。仕様策定段階の400Gビット イーサネット仕様に準じたMAC/PCSを実装し、2つの光インタフェースで送信したものを、残りの2つの光インタフェースで受信するループバック通信で動作させ、399.14Gビット/秒の帯域を実現した。

なお、デモでは、400Gビット イーサネット以外にもGTYを使用しHMCと接続し、メモリとの高速接続を実現した他、GTY8個を使用しリタイマなしのバックプレーン接続、伝送も行える構成となっている。

レイアウト使用率は50%を大幅に下回る

こうした高速伝送を行いながらも、ロジックセルの使用量は、XCVU095が持つ約94万ロジックセルの半分を大幅に下回る程度に収まり、「十分に、FPGAとして、さまざまなユーザーのアプリケーションを実装できる」(Saban氏)という。また今回のデモの開発には、「Vivado Design suite」を使用。Saban氏は、「400Gビット イーサネットのMAC/PCSが整理されたレイアウトで実装できており、開発環境としても十分に仕上がっていることが分かってもらえるだろう」とする。

そしてSaban氏は、「ES段階のデバイスで、400Gビット イーサネットも安定して動作させることができた。今後、出荷を開始していくVirtex UltraScaleファミリには、XCVU095で検証済みのGTYを横展開していくため、XCVU095同様、安定した動作を実現する高品質なデバイスとして提供できる」と語った。

関連記事

ザイリンクス優位は、20nm/16nm世代でも揺るがない

ザイリンクス優位は、20nm/16nm世代でも揺るがない

ザイリンクス日本法人は、現行の主力28nmプロセス採用FPGAの受注が好調だという。同社社長を務めるサム・ローガン氏に好調の理由や、今後、投入を本格化させる20nmプロセス採用FPGA製品のビジネス展望などを聞いた。 ザイリンクスが20nmプロセスFPGAの提供を開始、440万ロジックのVirtexも登場

ザイリンクスが20nmプロセスFPGAの提供を開始、440万ロジックのVirtexも登場

ザイリンクスは、20nmプロセスのFPGA「UltraScale」の提供を開始する。ミッドレンジの「Kintex UltraScale」ファミリとハイエンドの「Virtex UltraScale」ファミリだ。Virtex UltraScaleファミリでは、ロジックセルを440万個搭載した品種も用意する。 ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクス、20nmプロセスFPGAをテープアウト――製品戦略反映し呼称も「8」ではなく「UltraScale」

ザイリンクスは、20nmプロセス技術を用いたFPGAのテープアウト(設計完了)を発表した。同時に、20nmプロセス採用FPGAなどに適用する新世代アーキテクチャ「UltraScale」の概要も公表した。新プロセス、新アーキテクチャを採用した製品の出荷は2013年10〜12月を予定している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」