高性能デジタル編:PCとモバイルを牽引する最先端プロセッサ:徹底プレビュー「ISSCC2015の歩き方」(9)(2/2 ページ)

Samsungの「Exynos 7 Octa」とMediaTekの「MT6595」

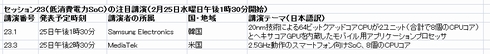

セッション23(サブテーマは「低消費電力SoC」)は、全体で3件の講演しかない。いわゆる「ハーフセッション」と呼ばれる、通常の半分の規模で実施されるセッションになっている。

ハーフセッションといっても内容はとても充実しており、3件中2件は注目すべき講演といえる。いずれも、スマートフォン向けのアプリケーション・プロセッサの開発成果である。

セッションの最初に、韓国のSamsung Electronicsが64ビットのアプリケーション・プロセッサを発表する(講演番号23.1)。発表の内容は、同社が「Exynos 7 Octa(旧名称はExynos 5433)」と呼ぶプロセッサの技術概要とみられる。ARMv8アーキテクチャの64ビットCPUコア「A57」を4個(bigコア)、同じく64ビットCPUコア「A53」を4個(LITTLEコア)、それぞれ内蔵する。高負荷時はbigコアを主に動かし、低負荷時はLITTLEコアを主に動かすことで高速動作と消費電力抑制のバランスをとる「big.LITTLEアーキテクチャ」を採用している。またGPUコア「ARM Mali-T760」を内蔵する。製造技術は20nm、9層金属配線である。

また米国と台湾のMediaTekが、LTEに対応した32ビットのアプリケーション・プロセッサを報告する(講演番号23.3)。内容は、同社が「MT6595」と呼ぶスマートフォン用アプリケーション・プロセッサの技術概要とみられる。ARMv7アーキテクチャの32ビットCPUコア「A17」を4個(bigコア)、同じく32ビットCPUコア「A7」を4個(LITTLEコア)、それぞれ内蔵する。このプロセッサもSamsungが発表したものと同様に、「big.LITTLEアーキテクチャ」を採用している。製造技術は28nm CMOS、シリコンダイ面積は89mm2である。

シリコンダイ固有の「指紋」をセキュリティに応用

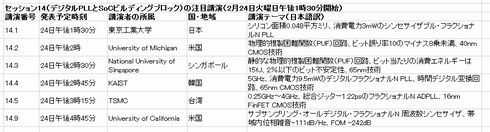

セッション14(サブテーマは「デジタルPLLとSoCビルディングブロック」)で最も興味深い講演は、「物理的複製困難関数(PUF:Physically Unclonable Function)」技術に関する研究成果だろう。半導体の製造工程で生じる、シリコンダイに固有な信号(これをPUF(パフ)と呼ぶ)をデジタルデータとして記憶し、指紋のような個人認証データとして利用する。PUFを利用すると、暗号技術を使わずとも、偽造防止や個体認証などを実現できることから、研究開発が活発である。既にICカード用シリコンダイでは、PUF技術が商用化されている。

ISSCC2015のこのセッションでは、米国のUniversity of Michigan(講演番号14.2)と、シンガポールのNational University of Singapore(講演番号14.3)がそれぞれ、PUF技術の研究成果を発表する。

この他セッション14では、デジタルPLLに関する講演が数多く予定されている。東京工業大学(講演番号14.1)、韓国のKAISTとSamsung Electronicsの共同研究グループ(講演番号14.4)、台湾TSMCとオランダDelft University of Technologyの共同研究グループ(講演番号14.5)、米国University of Californiaと台湾TSMCの共同研究グループ(講演番号14.9)がそれぞれ、フラクショナルN PLL技術を報告する。

関連記事

ARMが新プロセッサ「Cortex-M7」を発表、「コネクテッドカーを進化させる」

ARMが新プロセッサ「Cortex-M7」を発表、「コネクテッドカーを進化させる」

ARMは、マイコン向け32ビットプロセッサコア「Cortex-Mシリーズ」の新製品となる「Cortex-M7」を発表した。従来品の「Cortex-M4」と比べて、演算処理性能およびデジタル信号処理(DSP)性能を大幅に高めた。 超小型サーバを作るには――ARMプロセッサの選び方

超小型サーバを作るには――ARMプロセッサの選び方

ARMアーキテクチャを採用したプロセッサが多数、製品化されている。組み込み機器を設計する場合、どのプロセッサを選べばよいのだろうか。一般には、性能条件を満たした上で、必要な周辺機能を備えたSoCを選択すべきだとされているが、必要な仕様は組み込み機器によって千差万別だ。小型ARMサーバを製品化したぷらっとホームの事例「OpenBlocks」を紹介する。 タブレット向けプロセッサシェア、インテルが2位に躍進

タブレット向けプロセッサシェア、インテルが2位に躍進

モバイル端末向けチップの事業に注力してきたIntel。ようやく成果が出始めたようで、タブレット端末向けのアプリケーションプロセッサ市場で、Appleに次ぐ2位のシェアを獲得した。 クアルコムの次世代SoC「Snapdragon 810」、20nmプロセスへの移行が勝負に?

クアルコムの次世代SoC「Snapdragon 810」、20nmプロセスへの移行が勝負に?

Qualcomm(クアルコム)のモバイル機器向けSoCとして最新品種となる「Snapdragon 810」。多くの新しい機能を搭載し、プロセスも20nmを採用する。 Appleのプロセッサ「Aシリーズ」の系譜

Appleのプロセッサ「Aシリーズ」の系譜

Appleは、2013年中にも「iPhone 5S」と第5世代の「iPad」を発売するとみられている。これらには、プロセッサ「A7」「A7X」が搭載されるという見方がある。ここでは、これまでのiPhone/iPadに搭載されてきたプロセッサが、どんな進化を遂げてきたのかを振り返る。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速