デジタル電源向けコントローラIC、高性能で消費電力を従来比1/5に低減:電源設計 デジタル制御(2/2 ページ)

A-Dコンバータの高速化も

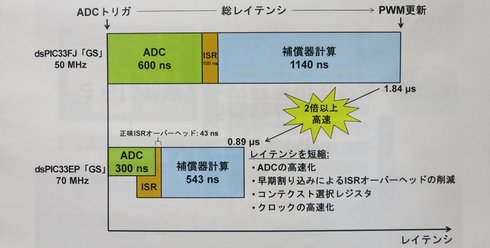

A-Dコンバータの高速化も図った。最大22チャネルのアナログ入力を備えた12ビットA-Dコンバータを最大5個内蔵している。3極3ゼロ(3P3Z)補償回路に適用した場合、A-Dコンバータのレイテンシは300nsで、総スループットは最大16Mspsを達成している。また、補償器計算のレイテンシは543nsとなった。

総レイテンシは0.89μsで、従来のdsPIC33FJ「GS」ファミリに比べると半分に短縮、同じく総スループットは4倍と高速だ。演算性能を高めたことで、電源回路のスイッチング周波数も、現行製品では最大500KHzまでしか対応できなかったが、dsPIC33EP「GS」ファミリでは、最大1MHzまで対応することが可能である。この他、CPUの負荷を軽減するデジタルコンパレータ機能や、12ビットD-Aコンバータ付きアナログコンパレータ、電流センサーの信号を直接入力することができるプログラマブルゲインアンプ、なども搭載した。

フラッシュメモリのライブアップデート機能も、dsPIC33EP「GS」ファミリで新たにサポートされた機能である。例えば容量が64kバイトのフラッシュメモリ搭載品では、32kバイトのメモリを2ブロック内蔵している。これによりシステム動作中であっても、利用していない片方のメモリブロックを使い、電源システム内部の更新プログラムをダウンロードすることができる。その後、ダウンロードした更新プログラムと既存のプログラムをわずか300ns以下で切り替えることが可能となった。これにより、システムを停止することができない通信インフラ用の電源などでも、動作状態のままファームウェアを更新することができる。

コントローラIC自体の消費電力低減とパッケージの小型化も大きな特長である。現行製品と同一の周波数で動作させた場合に、消費電力を約1/5に削減することが可能だという。100Wクラスのモジュールでは、ほぼ0.3W分の損失改善につながることになる。また、モジュールの放散熱量を4%削減することができる。パッケージサイズは外形寸法が4×4mm品も用意した。従来の6×6mm品に比べてボードの専有面積を半分以下に抑えることが可能となった。これによって、形状が親指大の1/8ブリックDC-DCコンバータ製品などへの搭載を容易とした。

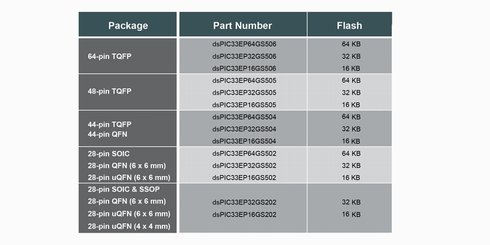

dsPIC33EP「GS」ファミリは、14製品を用意した。フラッシュメモリ容量で64kバイト品、32kバイト品、16kバイト品の3タイプがあり、パッケージは64端子/48端子/44端子のTQFP、44端子/28端子のQFN、28端子のSOIC、28端子のμQFNなどがある。サンプル出荷および量産出荷も始めた。価格は大口注文の場合で最低1.10米ドルである。

スタータキットも提供

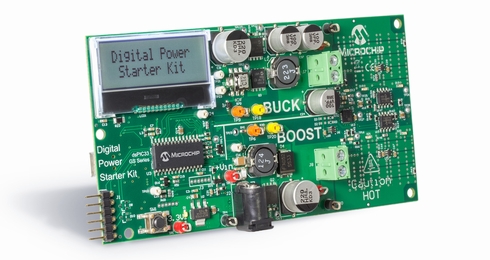

dsPIC33EP「GS」ファミリを用いて、デジタル電源の設計を比較的容易にするためのツール群も用意している。デジタル電源向けMPLABスタータキット「DM330017-2」を用いると、一般的な回路方式のデジタル電源を容易に評価することができる。オンボードでデバッグやプログラミングが可能である。価格は129.99米ドルとなっている。

また、回路性能を最適化する補償係数を容易に求めることができる無償ツール「Digital Compensator Design Tool」や、このツールと組み合わせて用いる「補償回路ソフトウェアライブラリ」および、ロイヤリティフリーの「dsPIC33リファレンスデザイン」などを提供する。

関連記事

マイクロチップがマイクレルを8億3900万ドルで買収

マイクロチップがマイクレルを8億3900万ドルで買収

マイクロチップ・テクノロジーは2015年5月7日(米国時間)、マイクレルを買収することで合意した。 2014年の世界半導体売上高ランキング、Qualcommと東芝は下方修正

2014年の世界半導体売上高ランキング、Qualcommと東芝は下方修正

Gartnerが、2014年の世界半導体売上高ランキングの最新版を発表した。首位はIntelで、2位にSamsung Electronics、3位にQualcommが続く。2015年1月に発表した暫定値(推定値)に比べ、売上高では、東芝とQualcommが下方修正されている。 マイクロチップの売上高が減少、背景に中国の成長鈍化

マイクロチップの売上高が減少、背景に中国の成長鈍化

Microchip Technology(マイクロチップ・テクノロジー)は、2014年7〜9月期における売上高の減少要因について、中国経済の鈍化を挙げた。同社は2014年10月に売上高予測を下方修正していて、その影響を受け、複数の半導体チップメーカーの株価が下がっている。 半導体業界は統廃合が進む、マイクロチップのCEOが言及

半導体業界は統廃合が進む、マイクロチップのCEOが言及

Microchip TechnologyのCEOであるSteve Sanghi氏は、「半導体業界の成長は鈍化しており、今後は半導体メーカーの統廃合が進む」と主張した。Microchipの戦略については「マイコンにARMコアを採用することはない」とし、8ビットマイコンのサポートにも注力していくという。 マイクロチップがSMSCを買収、車載分野への展開拡大も視野に

マイクロチップがSMSCを買収、車載分野への展開拡大も視野に

マイコン大手のMicrochip Technology(マイクロチップ)が、ネットワークやインタフェースの制御ICを手掛けるStandard Microsystems(SMSC)を約9億3900万米ドルで買収する。この買収は、マイクロチップが車載分野に参入する足掛かりになるかもしれない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化

デジタル電源向けMPLABスタータキット「DM330017-2」の外観

デジタル電源向けMPLABスタータキット「DM330017-2」の外観