プレーナ型NANDフラッシュの微細化の限界:メモリ各社の製品から探る(2/4 ページ)

» 2015年06月23日 09時30分 公開

[Kevin Gibb(TechInsights),EE Times]

ダブルパターニングの2つのアプローチ

ダブルパターニング技術では、2種類のアプローチを適用することができる。LELE(Litho-Etch-Litho-Etch)方式のダブルパターニングは、論理プロセスに適用される場合が多い。もう1つのSADP(Self Aligned Double Patterning)方式は、メモリメーカーで採用されている。ただしこの方式は、 現行の16nmプロセス世代までのNANDフラッシュには効果的だったが、10nmクラスには適さない可能性がある。

それでも今のところ、プレーナ型NANDフラッシュメモリを10nm世代まで微細化することが最も重要な課題だと考えられている。このため、3D NANDフラッシュメモリの開発に向けた取り組みが加速する結果となった。図1では、完全を期すために、SamsungのV-NANDも示してある。また、東芝やSK-Hynix、Micronも近々、3D NAND製品を発表するとみられている。

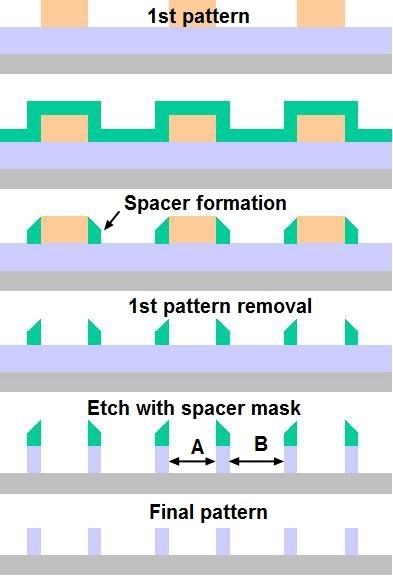

ダブルパターニングは、16nmプロセスのNANDフラッシュの製造に必須の技術になっている。メモリーメーカーは、アクティブコントロールゲートやフローティングゲート、ビット線パターニングにSADPを用いている。図2は、イニシャルパターンの作製から、側壁(サイドウォール)スペーサエッチングを経て、ダブルパターニングに至るまでの、SADPのフローについて図解している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

図2 SADPのフロー 出典:Wikipedia

図2 SADPのフロー 出典:Wikipedia