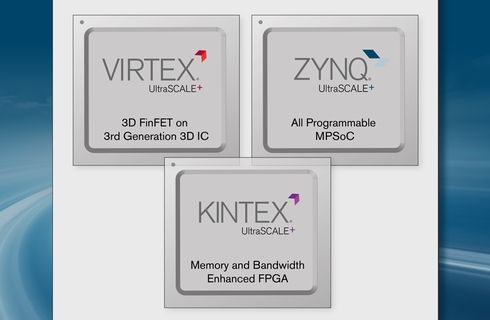

ザイリンクス、16nmハイエンド「Virtex」を出荷:16nm UltraScale+ファミリ全てが入手可能に

Xilinx(ザイリンクス)は、TSMCの16FF+(16nm FinFET プラス)プロセスを用いたハイエンド向けFPGA「Virtex UltraScale+ FPGA」を顧客向けに出荷を開始したと発表した。

Xilinx(ザイリンクス)は2016年1月28日(米国時間)、TSMCの16FF+(16nm FinFET プラス)プロセスを用いたハイエンドFPGA「Virtex UltraScale+ FPGA」を発表した。

これにより、同社が展開するCPUコア搭載型FPGA「Zynq UltraScale+ MPSoC」と「Kintex UltraScale+ FPGA」に続いて、16nmプロセスを採用した「UltraScale+」3つのファミリ全ての入手が可能となった。出荷を開始しているUltraScale+は既に、60社以上の顧客にデバイス/ボードの出荷を開始しているという*)。

*)関連記事:ザイリンクス、16nm世代FPGA「Zynq」を出荷

データセンターや航空宇宙分野向け

Virtex UltraScale+ FPGAは、32Gバイト(GB)のトランシーバー、PCI Express Gen 4内蔵コア、UltraRAMなどの機能を搭載。データセンターやテラビットワイヤード通信、航空宇宙/防衛などの分野で要求される性能や集積度を備えているとした。

プログラマブル製品グループ担当エグゼクティブバイスプレジデントのVictor Peng氏は、「ザイリンクスは、28nm、20nm、16nm プロセスと3世代続けて業界に先駆けて、最先端製品を発表した。これは、業界で最先端となる製品を最も早く市場に提供するという、ザイリンクスの持続的な取り組みを表すものである」とコメントしている。

Virtex UltraScale+ FPGAは、既に出荷を開始。同社は、「UltraScale+ ポートフォリオは、28nmデバイスファミリと比較して、単位ワット当たりのシステム性能を2~5倍向上させることを実現した」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -- 闕ウ�サ髫補�豼�陝���ス逧Г邵コ�ョ鬩包スク隰壽ァュ縲堤クコ�ッ闕ウ讎企ヲ呵崕�スツ竏ャ�ィ蝓滂スク�ャ�ス蜀怜アョ髫墓じ縺�ケ晏干ホ懃クコ�ョ雎ク驛�スイ�サ鬮ョ�サ陷牙ク呻ス定ャ壻サ」竏エ郢ァ迢暦スァ蛟ゥ�ィ�」

- SAR ADC郢ァ蜑�スス�ソ騾包スィ邵コ蜉ア笳�坎蝓滂スク�ャ郢ァ�「郢晏干ホ懃クイ竏壹☆郢ァ�ー郢晉ソォホ晉ケ昶�縺臥ケ晢スシ郢晢スウ邵コ�ョ郢ァ�ソ郢ァ�、郢晄コ佩ヲ郢ァ�ー邵コ�ォ雎包スィ隲「蜀励○邵コ繧�ス�

- 郢ァ�ケ郢ァ�、郢晢ソス繝。郢晢スウ郢ァ�ー鬮ョ�サ雋��縲竪aN�ス閧イ�ェ雋槫密郢ァ�ャ郢晢スェ郢ァ�ヲ郢晢ソス�ス逕サ讖ソ髯ヲ阮呻ス定崕�ゥ騾包スィ邵コ蜷カ�玖撻�エ陷キ蛹サ竊馴蔓�ス�ス邵コ蜷カ竏狗クコ蝣コ�コ蛹コ豌�

- [EE Times Japan驍ア�ィ鬮ョ�スホ咯 陷企宦�ー諠ケ�ス轣倩�驕会スセ 隶鯉スュ驍オ�セ邵コ�セ邵コ�ィ郢ァ竏堋�ス2025陝キ�エ3隴帛沺謔�ィセ螢ス謔�クイ�ス

- �趣ス」�取ウ梧「妁DC郢ァ雋櫁懸騾包スィ邵コ蜷カ�矩坎蝓滂スク�ャ�ス蜀怜アョ髫墓じ縺�ケ晏干ホ懃クイ竏晢ソス隴ォ闊鯉ス�崕�カ陟包ス。邵コ�ョ郢ァ�ソ郢ァ�、郢晄コ佩ヲ郢ァ�ー郢ァ蛛オ竊千クコ�ス�ィ蛹サ�具ソス�ス

Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- TSMCがGaNファウンドリー事業から撤退へ、NavitasはPSMCと提携で対応

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

- 25年5月の世界半導体市場は全地域で成長、19.8%増の590億ドルに

- 危うい再建計画 Wolfspeed、CHIPS法補助金で再生図るか

- 半導体製造ラインの立ち上げ迅速に、日本IBMが京都に開発拠点

- Qualcommの狙いは何なのか、やたらと「高い」Alphawave買収額

- 「DRAM生産の4割を米国で」 Micronを待ち受ける過酷な競争

- 22nmプロセス採用でMRAM内蔵、ルネサスがエッジAI特化の新マイコン

放送機器/業務用AV機器向けFPGA事業を強化

放送機器/業務用AV機器向けFPGA事業を強化 Stratix 10メカニカルサンプルを公開 アルテラ

Stratix 10メカニカルサンプルを公開 アルテラ Artix-7 35T FPGA評価キット、アヴネットが発売

Artix-7 35T FPGA評価キット、アヴネットが発売 たった5ドルで手に入る!? 10mm角の8ピンFPGAモジュール

たった5ドルで手に入る!? 10mm角の8ピンFPGAモジュール