ルネサス 90nm BCDプロセス混載可能なフラッシュ:次世代車載マイコンに適用へ(2/3 ページ)

読み出し時に選択ゲートに正電圧を印加しない

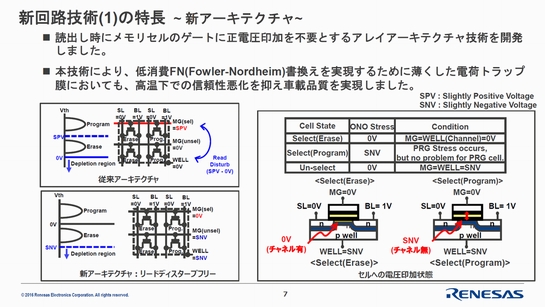

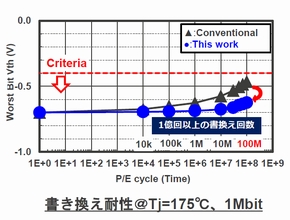

書き換え耐性1億回という信頼性は、主に2つの回路技術で実現した。1つは、読み出し時にメモリセル選択ゲートへの正電圧印加を不要にするアレイアーキテクチャ技術だ。

電荷(チャージ)トラップ方式のフラッシュメモリの場合、FN(Fowler-Nordheim)トンネル効果を利用して絶縁膜(電荷トラップ膜)に挟まれた記憶領域に電荷を出し入れする。小さな電力で、FNトンネル効果を起こすには、電荷トラップ膜を薄くする必要があるが、薄くすると信頼性が悪化する。具体的には、読み出し時に、メモリ選択ゲート(MG)に正電圧を印加する際に生じる電位差が、電荷トラップ膜にストレスを与え、劣化(しきい値電圧が下がる/リードディスターブ)の原因となる。

これに対し、ルネサスのアレイアーキテクチャは、読み出し時にメモリ選択ゲート(MG)に正電圧を印加せず、0Vを与える。代わりに、サブストレート側(WELL)に負電圧を印加することで、読み出しに必要な電位差を作り出す。この場合にも、電荷トラップ膜に電位差が加わることになるが「ほぼ劣化要因とはならなくなった」(ルネサス)とする。

電界の印加を高度に緩和する技術

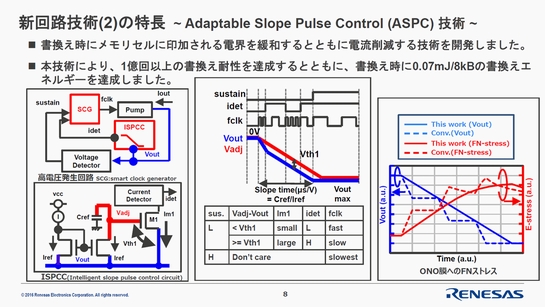

もう1つの信頼性向上技術は、書き換え時にメモリセルに印加される電界を緩和する「Adaptable Slope Pulse Control」(ASPC)技術だ。

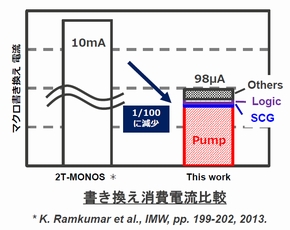

メモリセルは急な電界の変化に弱く、段階的に電界を与え、メモリセルへのストレスを軽減する手法が有効だ。既に、多くのフラッシュメモリで段階的に電界を加える技術が用いられている。「一般的なフラッシュメモリは、数段階の電界切り替えパルス(書き換えパルス)生成でも十分な信頼性を確保できたが、より高い信頼性を得るには、さらにスムーズなパルス生成が必要だった」とし、ルネサスは高速なパルス生成で、なだらかに電界を与えていく回路を構築。また、メモリセルの容量などの状況を検知し、電界の印加を最適化する回路も搭載。同回路により、無駄な電界印加を避け信頼性を高めるとともに、書き換えに必要な消費電流を抑えることに成功。書き換え時の消費電流は98μAで「従来の書き換え電流よりも2桁少ない」(ルネサス)とする。8Kバイト容量のメモリセルの書き換えに必要なエネルギー量は0.07mJ(128Kバイト容量試作チップでの測定結果)を実現している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速