3D NAND僼儔僢僔儏偺嫞憟偼寖壔傊丗Micron偑乽ISSCC 2016乿偱768G價僢僩昳傪敪昞乮2/3 儁乕僕乯

僠儍乕僕僩儔僢僾偐丄僼儘乕僥傿儞僌僎乕僩偐

丂偙傟傑偱丄3D NAND僼儔僢僔儏偱偼僠儍乕僕僩儔僢僾曽幃偑嵦梡偝傟偰偒偨丅偩偑丄摨曽幃偼僾儗乕僫宆NAND僼儔僢僔儏偵揔梡偝傟傞僼儘乕僥傿儞僌僎乕僩曽幃偲斾傋傞偲崅僐僗僩偱偁傞丅

丂Handy巵偼丄乽僠儍乕僕僩儔僢僾曽幃偱丄僾儗乕僫宆NAND僼儔僢僔儏偲僐僗僩嫞憟椡偺偁傞3D NAND僼儔僢僔儏傪惢憿偱偒傞偲偼峫偊偵偔偄丅Micron偑奐敪偟偨僼儘乕僥傿儞僌僎乕僩曽幃偺3D NAND僼儔僢僔儏偼丄偙偆偟偨忬嫷傪岲揮偝偣傞偙偲偑偱偒傞偲婜懸偝傟傞偑丄寢榑傪弌偡偵偼帪婜彯憗偩乿偲弎傋偰偄傞丅

丂Samsung偼丄僼儔僢僔儏儊儌儕巗応偱34.1亾偺僔僃傾傪屩傝丄摨巗応傪儕乕僪偟偰偄傞丅Micron偼搶幣丄SanDisk偵師偖戞4埵偱丄僔僃傾偼14.6亾偱偁傞丅

丂Handy巵偼丄乽Samsung偺3D NAND僼儔僢僔儏亀V-NAND亁偼丄攧傝忋偘傪弴挷偵怢偽偟偰偄傞丅検嶻偵傛偭偰丄摨媄弍偑書偊傞僐僗僩柺偱偺壽戣傪崕暈偟偨偄峫偊偩丅V-NAND偺攧傝忋偘偑寴挷偱偁傞偙偲偼丄媄弍儕乕僟乕偲偟偰偺摨幮偺僀儊乕僕偵傕栶棫偭偰偄傞丅偩偑丄媄弍儕乕僟乕偱偁傞偙偲傪恀偵徹柧偡傞偵偼丄懡妟偺僐僗僩傪搳偠傞昁梫偑偁傞偩傠偆乿偲巜揈偟偰偄傞丅

偄偢傟偼100憌埲忋偵愊憌

丂堦曽偺Samsung傕丄ISSCC 2016偱丄3D NAND僼儔僢僔儏偵偮偄偰愢柧偟偰偄傞丅

丂儊儌儕僙儖傪悅捈曽岦偵48憌廳偹偨戞3悽戙偺3D NAND僠僢僾偼丄摨幮偑2015擭偵敪昞偟偨32憌偺儗僀儎乕傪帩偮媽昳庬偲斾傋偰丄枾搙偑2攞崅偄偲偄偆丅摨幮偺宱塩姴晹偼埲慜偵丄乽偄偢傟偼丄100憌埲忋偵憹傗偡偙偲偑壜擻偩乿偲岅偭偰偄傞丅

丂Samsung偺榑暥偺挊幰偱偁傞Dongku Kang巵偼丄乽惉岟偺尞偼丄柺枾搙偵偁傞乿偲弎傋丄Apple偺壒妝僾儗乕儎乕乽iPod乿偑丄傛傝懡偔偺儊儌儕傪搵嵹偟偨偙偲偵傛偭偰丄偄偐偵嫞崌懠幮惢昳傪懪偪晧偐偡偙偲偑偱偒偨偐傪愢柧偟偨丅

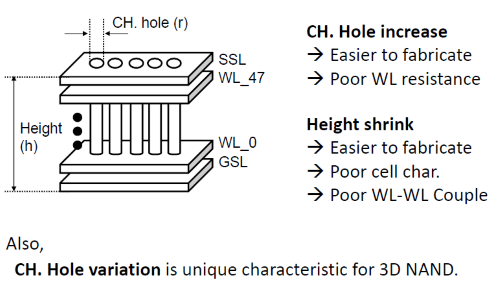

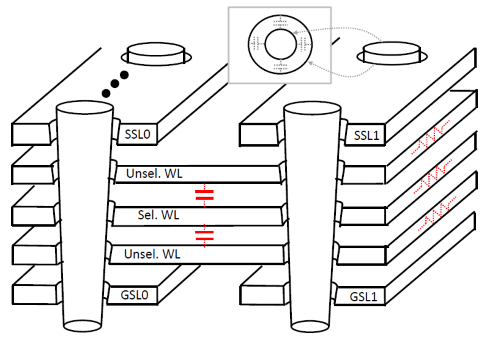

丂偙偺傛偆側NAND僼儔僢僔儏傪惢憿偡傞忋偱壽戣偺1偮偲側偭偰偄傞偺偑丄奺憌傪捠傞傛偆偵廲挿偺寠傪僄僢僠儞僌偡傞偙偲偵傛偭偰丄憌摨巑傪愙懕偟丄偦偺寠偵僀儞僞乕僐僱僋僩傪幚憰偡傞偲偄偆揰偩丅Kang巵偼丄乽斾妑揑戝偒側僠儍儞僱儖儂乕儖偼娙扨偵嶌傞偙偲偑偱偒傞偑丄儚乕僪慄掞峈偑掅壓偡傞偲偄偆栤戣偑惗偠傞乿偲弎傋傞丅

丂SanDisk偺憂愝幰偱偁傝丄僼儔僢僔儏儊儌儕暘栰偺愭嬱幰偱傕偁傞Eli Harari巵偼丄乽崱屻丄Samsung偺僠儍乕僕僩儔僢僾曽幃偲丄Micron Technology偺僼儘乕僥傿儞僌僎乕僩曽幃偺偳偪傜偺媄弍偑晛媦偟偰偄偔偺偐丄崱偺偲偙傠偼傑偩暘偐傜側偄丅偟偐偟丄僼儘乕僥傿儞僌僎乕僩偼旕忢偵擄偟偄媄弍偱偁傞偙偲偐傜丄巹偲偟偰偼僠儍乕僕僩儔僢僾偺曽偑桳椡偩偲妋怣偟偰偄傞乿偲弎傋偰偄傞丅摨巵偼丄ISSCC 2016偺島墘偵嶲壛偟丄嵟慜楍偵嵗偭偰拲堄怺偔帹傪孹偗偰偄偨丅

丂堦曽偱Tanaka巵偼丄乽僼儘乕僥傿儞僌僎乕僩曽幃偼丄僾儗乕僫宆NAND僼儔僢僔儏偵偍偄偰廫暘偵妋棫偝傟偨媄弍偱偁傝丄Micron偲SanDisk偺椉幮傕悢懡偔偺娭楢摿嫋傪曐桳偟偰偄傞乿偲巜揈偡傞丅摨巵偼丄偐偮偰搶幣偱NAND僼儔僢僔儏偺愝寁傪扴摉偟偨宱楌傪帩偮丅

丂Harari巵偼丄婛偵SanDisk傪戅怑偟偰偄傞偙偲偐傜丄乽偦偺傛偆側揰偵娭偟偰偼丄巹偺抦幆偑捛偄晅偄偰偄側偄偐傕偟傟側偄乿偲弎傋偨丅偦傟偱傕摨巵偼丄尰嵼傕嬈奅偵偍偄偰惛椡揑側妶摦傪懕偗偰偄傞偲偄偆丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

- 2023擭偺悽奅敿摫懱攧忋崅儔儞僉儞僌僩僢僾20丄NVIDIA偑弶偺2埵偵

- 拞崙惌晎偺乽Intel乛AMD嬛巭椷乿丄拞崙婇嬈傊偺嫮偄捛偄晽偵

- JDI丄師悽戙桳婡EL僨傿僗僾儗僀乽eLEAP乿傪24擭12寧偵検嶻奐巒傊

- 廳検偼僋僕儔媺両丂挻嫄戝側崅NA EUV憰抲偺愝抲傪Intel偑岞奐

- 慡屌懱僫僩儕僂儉揹抮偺検嶻壔偵岦偗偨怴崌惉僾儘僙僗傪奐敪丄戝嶃岞棫戝

- 僷儚乕敿摫懱岦偗僂僄僴乕巗応丄2035擭偵1挍墌戜傊

- 廇嬈恖堳偺4妱偑婣娨慻丄儖僱僒僗峛晎岺応偑10擭偺帪傪宱偰嵞壱摥

- Intel偑崅NA EUV憰抲偺慻傒棫偰傪姰椆丄Intel 14A偐傜偺摫擖偵岦偗偰慜恑

- 傢偢偐3屄偺LSI偱儌僶僀儖挻壒攇恌抐憰抲傪幚尰丄僜僔僆僱僋僗僩

- 慡屌懱Li僀僆儞揹抮梡僼僢壔暔屌懱揹夝幙傪奐敪

Samsung偑敪昞偟偨丄悅捈宆3D NAND偺棙揰偲壽戣

Samsung偑敪昞偟偨丄悅捈宆3D NAND偺棙揰偲壽戣 僀儞僞乕僐僱僋僩偺宍忬傪偳偆嵟揔壔偡傞偐偑丄Samsung偺壽戣偩偲偄偆

僀儞僞乕僐僱僋僩偺宍忬傪偳偆嵟揔壔偡傞偐偑丄Samsung偺壽戣偩偲偄偆