乽SEMICON West 2016乿丄7nm悽戙埲崀偺儕僜僌儔僼傿媄弍乮Applied Materials曇乯丗暉揷徍偺僨僶僀僗捠怣乮92乯乮1/2 儁乕僕乯

Applied Materials偺島墘偱偼丄MOSFET偺旝嵶壔儘乕僪儅僢僾偲丄旝嵶壔偺庤朄偍傛傃壽戣偑夝愢偝傟偨丅7nm悽戙偺FinFET偱偼丄僼傿儞傪嫹偔丄崅偔偡傞偲偲傕偵僐儞僞僋僩梡偺嬥懏嵽椏傪曄偊傞昁梫偑弌偰偔傞丅FinFET偺尷奅偑尒偊巒傔傞5nm悽戙偱偼丄旝嵶壔偺庤朄偲偟偰庡偵2偮偺慖戰巿偑偁傞丅

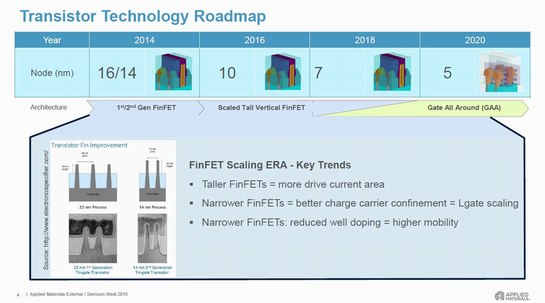

儘僕僢僋梡僩儔儞僕僗僞偺旝嵶壔儘乕僪儅僢僾

丂敿摫懱惢憿憰抲偲敿摫懱惢憿梡嵽椏偵娭偡傞杒暷嵟戝偺揥帵夛乽SEMICON West 2016乿偑7寧12擔乣14擔偵暷崙僇儕僼僅儖僯傾廈僒儞僼儔儞僔僗僐偺儌僗僐乕儞僙儞僞乕乮Moscone Center乯偱奐嵜偝傟偨丅12擔偵偼乽FORUM乿乮僼僅乕儔儉乯偲徧偡傞暪愝偺島墘夛偑偁傝丄愱栧僥乕儅偵娭偡傞夝愢傗揥朷側偳傪悢懡偔偺尋媶幰傗媄弍幰丄宱塩幰側偳偑敪昞偟偨丅

丂拞偱傕嫽枴怺偐偭偨偺偼丄師悽戙偺儕僜僌儔僼傿媄弍傪揥朷偡傞僼僅乕儔儉偱偁傞丅屵慜拞偵偼乽Lithography: Charting a Path, or Paths, Between Nodes 10 and 5乿偲戣偡傞僼僅乕儔儉偑丄屵屻偵偼乽Node 10 to node 5 - Dealing with the Slower Pace of Traditional Scaling乿偲戣偡傞僼僅乕儔儉偑奐嵜偝傟偨丅杮僐儔儉偱偼傑偢丄屵慜偺僼僅乕儔儉偐傜庡偩偭偨島墘偺奣梫傪偛曬崘偟偨丅慜乆夞偐傜偼丄屵屻偺僼僅乕儔儉偐傜庡側島墘偺奣梫傪偛徯夘偟偰偄傞丅

丂崱夞偼丄敿摫懱惢憿憰抲戝庤偺Applied Materials偱Technical Projects, Transistor and Interconnect Group偺僔僯傾僨傿儗僋僞乕傪柋傔傞Michael Chuzik巵偺島墘奣梫傪偛曬崘偡傞丅島墘僞僀僩儖偼乽Fins and Wires, How Do We Get To 5nm ?乿偱偁傞丅島墘偱偼丄CMOS儘僕僢僋傪巟偊傞MOSFET乮僩儔儞僕僗僞乯偺旝嵶壔儘乕僪儅僢僾傪帵偟丄旝嵶壔偺庤朄偲壽戣傪愢柧偟偰偄偭偨丅

丂尰峴偺嵟怴悽戙偱偁傞16乛14nm悽戙偺儘僕僢僋梡僩儔儞僕僗僞偵偼FinFET乮僼傿儞FET乯偑巊傢傟偰偄傞丅僔儕僐儞偺僠儍儞僱儖傪僼傿儞忬偵偡傞偙偲偱丄旝嵶壔傪壜擻偵偟偨僩儔儞僕僗僞媄弍偱偁傞丅

丂10nm悽戙偱偼丄FinFET偺僼傿儞傪嫹偔丄崅偔偡傞偙偲偱旝嵶壔傪幚尰偡傞偙偲偑妋幚偵側偭偰偄傞丅僼傿儞傪嫹偔偟偰僼傿儞偺僺僢僠傪媗傔傞偙偲偱丄婎杮悺朄傪抁偔偡傞丅摨帪偵僂僄儖偺僪乕僺儞僌擹搙偑壓偑傝丄僉儍儕傾偺堏摦搙偑忋偑傞丅僼傿儞偺崅偝傪忋偘傞偙偲偼丄僩儔儞僕僗僞偺揹棳嬱摦擻椡傪岦忋偝偣傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

- 2023擭偺悽奅敿摫懱攧忋崅儔儞僉儞僌僩僢僾20丄NVIDIA偑弶偺2埵偵

- 拞崙惌晎偺乽Intel乛AMD嬛巭椷乿丄拞崙婇嬈傊偺嫮偄捛偄晽偵

- 廇嬈恖堳偺4妱偑婣娨慻丄儖僱僒僗峛晎岺応偑10擭偺帪傪宱偰嵞壱摥

- 擔杮揱摑偺乽榓憰暱乿偑僸儞僩偵丂敿摫懱偺崅搙側擬娗棟偵偮側偑傞媄弍

- JDI丄師悽戙桳婡EL僨傿僗僾儗僀乽eLEAP乿傪24擭12寧偵検嶻奐巒傊

- 儖僱僒僗峛晎岺応偑偄傛偄傛嵞壱摥丂幠揷幮挿乽僷儚乕敿摫懱偺愴棯揑嫆揰偵乿

- Raspberry Pi偑AI僇儊儔儌僕儏乕儖敪攧傊丄僜僯乕偺AI張棟婡擻搵嵹僙儞僒乕嵦梡

- 敿摫懱惢憿憰抲偺斕攧妟丄2023擭偼1063壄僪儖偱慜擭斾1.3亾尭

- 慡屌懱僫僩儕僂儉揹抮偺検嶻壔偵岦偗偨怴崌惉僾儘僙僗傪奐敪丄戝嶃岞棫戝

- Rapidus丄僔儕僐儞僶儗乕偵怴夛幮愝棫丂AI敿摫懱偺屭媞奐戱傪壛懍