SanDiskが語る、ストレージ・クラス・メモリの概要:福田昭のストレージ通信(44) 抵抗変化メモリの開発動向(3)(1/2 ページ)

ストレージ・クラス・メモリ(SCM)は、次世代の半導体メモリに最も期待されている用途である。今回は、このSCMの要件について、記憶密度やメモリアクセスの制約条件、メモリセルの面積の観点から紹介する。

| 抵抗変化メモリの開発動向バックナンバー: | |

|---|---|

| (1) | SanDiskが語る、半導体不揮発性メモリの開発史 |

| (2) | SanDiskが語る、コンピュータのメモリ階層 |

ストレージ・クラス・メモリ(SCM)の具体的な位置付け

半導体メモリの研究開発に関する国際学会「国際メモリワークショップ(IMW:International Memory Workshop)」のショートコース(2016年5月15日)から、SanDiskによる抵抗変化メモリ(ReRAM)の研究開発動向に関する講演概要をご紹介している。今回はシリーズの3回目に相当する。

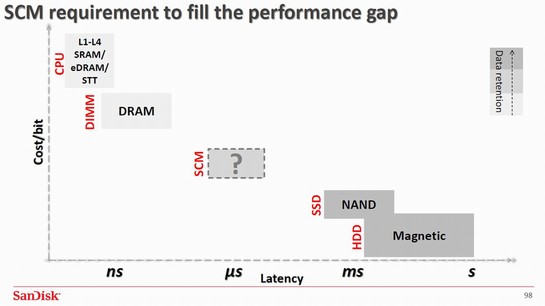

講演者はスタッフエンジニアのYangyin CHEN氏、講演タイトルは「ReRAM for SCM application」である。タイトルにあるSCMとはストレージ・クラス・メモリ(storage class memory)の略称で、性能的に外部記憶装置(ストレージ)と主記憶(メインメモリ)の間に位置するメモリとされる。ここで性能とは、メインメモリよりもコスト(記憶容量当たりのコスト)が低く、ストレージよりも高速であることを意味する。

SCMは、次世代の半導体メモリに最も期待されている用途である。SCMの位置を占める次世代半導体メモリの候補は主に3つ。抵抗変化メモリ、磁気メモリ、相変化メモリである。いずれも不揮発性メモリであるとともに、大容量化を実現可能とされる。

本シリーズの2回目である前回は、コンピュータのメモリ階層に関する講演パートをご紹介した。今回は、メモリ階層におけるSCM(ストレージ・クラス・メモリ)の位置付けについて講演したパートの概要をご報告する。

DRAMより低いコスト、NANDフラッシュよりも高速なアクセス

前回の最後でふれたように、西暦2020年ごろにはコンピュータ(PCやサーバなど)のメモリ階層で、DRAMとSSDのギャップを埋めるメモリ層、SCMが登場するとされる。SCMに要求されるのは、記憶容量当たりのコストではDRAMよりも低く、メモリアクセスの遅延時間(レイテンシ)はSSDよりも2桁〜3桁程度は短いことだ。

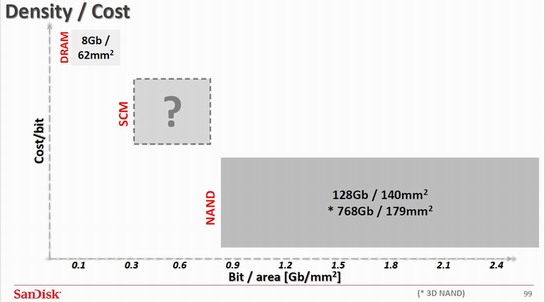

記憶密度は0.3Gbit/mm2〜0.8Gbit/mm2

記憶容量当たりのコストは、シリコンダイ面積当たりの記憶容量で置き換えられる。8Gbit DRAMのシリコンダイ面積を62mm2とすると、シリコンダイ面積(平方ミリ)当たりの記憶容量は0.13Gbitとなる。一方で128Gbit NANDフラッシュメモリ(プレーナ技術)のシリコンダイ面積を140mm2とすると、シリコンダイ面積(平方ミリ)当たりの記憶容量は0.9Gbitとなる。

SCMに要求されるのはDRAMとNANDフラッシュメモリの間、すなわちシリコンダイ面積(平方ミリ)当たりの記憶容量でおよそ0.3Gbit〜0.8Gbitの範囲である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に