不揮発SRAMでプロセッサの待機時電力を大幅削減:不揮発性パワーゲーティング(2/2 ページ)

NV-SRAMの特性評価結果

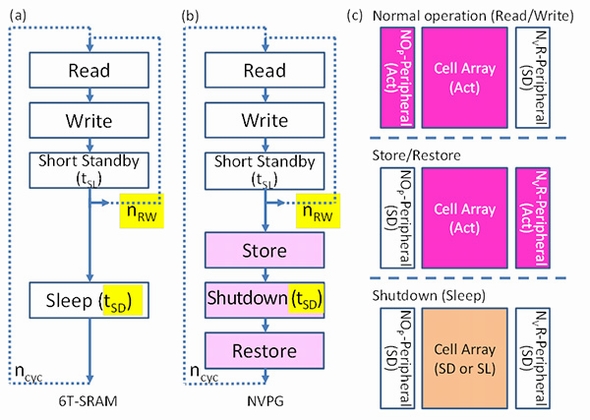

試作したNV-SRAMの特性評価も行った。NVPGでは、セルアレイの全ビットを読み出し/書き込み後に、スリープモード(時間はtSL)となる。これをnRW回繰り返し、MTJに書き込みしてからシャットダウン(時間tSD)し、その後復帰させる。通常のSRAMだと待機時は全てスリープモードとなる。通常動作用と不揮発記憶用の周辺回路を使用しない場合は、電源遮断状態とした。

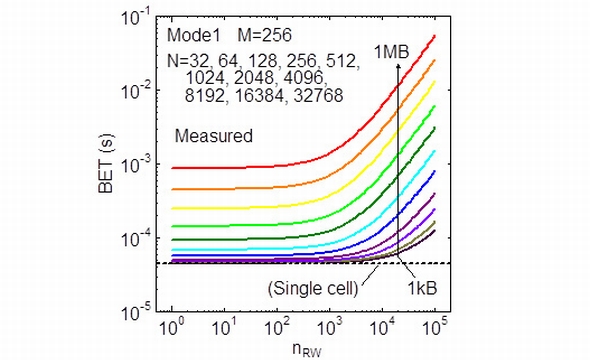

パワーゲーティングの性能指標となるBET(Break-Even Time)から、NV-SRAMのエネルギー性能を解析した。BETは電源遮断によってエネルギーを削減できる最低の電源遮断時間である。BETはnRWとアレイサイズ(Mビット×Nライン)によって変化するという。BETがnRWに依存しない領域では、アレイサイズが大きいほどBETが増大する。BETがnRWに依存して増大する領域では、不揮発記憶用周辺回路のリーク電流に対する依存度が高く、アレイサイズとともに増大するという。

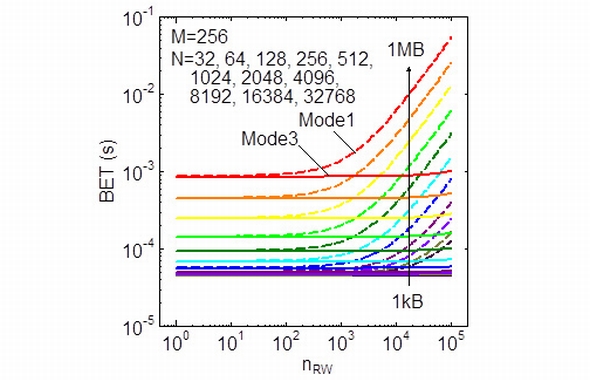

nRWに依存して増大するBETは、不揮発記憶用周辺回路のリーク電流を削減することでその増大を抑えることができる。今回は、SOTBの基板バイアスを用いて、BETの増加を大幅に抑制している。

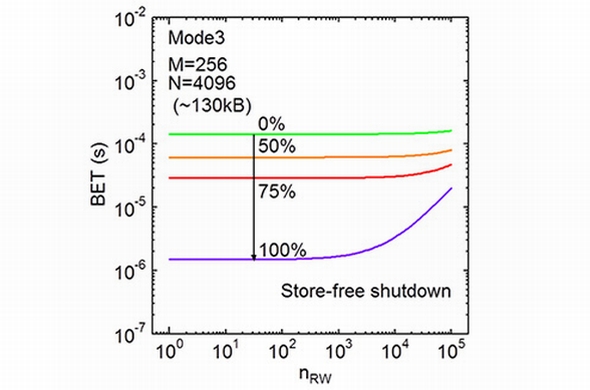

ラインNに依存して増大するBETは、「ストアフリーシャットダウン」と呼ぶアーキテクチャを用いることで削減可能だという。MTJに記憶されている内容が、SRAM部で記憶している内容と一致すれば、MTJへの書き込みをスキップして電源を遮断する仕組みである。

今回開発したNV-SRAM技術は、各階層のキャッシュに加え、レジスターファイルや、フリップフロップの不揮発化など、コア内にある他の記憶回路にも拡張できるという。開発したNVPG技術をコアレベルのパワーゲーティングに適用することで、メニーコアプロセッサにおける待機時電力を大幅に削減することが可能となる。

関連記事

希少元素を使わない赤く光る窒化物半導体を発見

希少元素を使わない赤く光る窒化物半導体を発見

東京工業大学と京都大学の共同研究チームは2016年6月、希少元素を使わずに、赤色発光デバイスや太陽電池に応用できる新たな窒化物半導体を発見、合成したと発表した。 高周波圧電共振器の課題を解決する回路

高周波圧電共振器の課題を解決する回路

東京工業大学と情報通信研究機構(NICT)は2016年6月15日、シリコン上に集積できる高周波圧電共振器による位相同期回路(PLL)を、無線モジュールの水晶発振器を置き換え可能な性能で実現する技術を開発したと発表した。 情報漏えいの危険がない、分散ストレージを開発

情報漏えいの危険がない、分散ストレージを開発

情報通信研究機構(NICT)は東京工業大学と共同で、分散ストレージシステムにおいて認証、伝送、保存というすべての工程で情報理論的安全性を担保するシステムの実証実験に成功した。計算機の処理能力が飛躍的に向上しても情報漏えいの危険を回避できる技術だという。 毎秒56Gビットの無線伝送、CMOS回路で実現

毎秒56Gビットの無線伝送、CMOS回路で実現

富士通は、「ワイヤレス・テクノロジー・パーク(WTP)2016」で、富士通研究所と東京工業大学が開発した、毎秒56Gビットの無線伝送を可能とするCMOS無線送受信チップとそのモジュール技術を紹介した。 40GHz帯/60GHz帯協調による無線網の実証に成功

40GHz帯/60GHz帯協調による無線網の実証に成功

ソニーやKDDI研究所などは2016年2月29日、40GHz帯と60GHz帯を協調させた次世代高速ワイヤレスアクセスネットワーク構築し、実証に成功したと発表した。 低閾値電圧の有機Trを実現する化合物を安定合成

低閾値電圧の有機Trを実現する化合物を安定合成

東京工業大学は2016年5月、閾(しきい)値電圧の低い有機トランジスタ(Tr)として機能する化合物を安定的に合成する手法を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- Intelの最新AI戦略と製品 「AIが全てのタスクを引き継ぐ時代へ」

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

評価に用いたベンチマークシーケンスと各回路ブロックの動作モード 出典:東京工業大学

評価に用いたベンチマークシーケンスと各回路ブロックの動作モード 出典:東京工業大学 BETのnRW依存性 出典:東京工業大学

BETのnRW依存性 出典:東京工業大学 SOTBの基板バイアスを用いて、周辺回路のリーク電流を削減した場合のBETのnRW依存性(実線) 出典:東京工業大学

SOTBの基板バイアスを用いて、周辺回路のリーク電流を削減した場合のBETのnRW依存性(実線) 出典:東京工業大学 ストアフリーシャットダウンの効果を示すグラフ 出典:東京工業大学

ストアフリーシャットダウンの効果を示すグラフ 出典:東京工業大学