東工大、微細化でIGBTのオン抵抗を半減:3分の1スケーリングで実証

東京工業大学は、微細加工技術によりシリコンパワートランジスタの性能を向上させることに成功したと発表した。従来に比べオン抵抗を約50%低減できることを実証した。

IGBTの耐圧は維持、ゲート電圧は5Vに低下

東京工業大学科学技術創成研究院未来産業技術研究所の筒井一生教授らは2016年12月、微細加工技術により、シリコンパワートランジスタの性能を向上させることに成功したと発表した。従来に比べオン抵抗を約50%低減できることを実証した。

パワートランジスタ市場では、価格などの面からシリコンIGBT(Si Insulated Gate Bipolar Transistor)が占める比率は依然として高い。ところが、性能面ではオン抵抗の低減による低損失化などが課題となっている。今回は、微細化(スケーリング)による高性能化に注目し、3分の1スケーリングのSi-IGBTを作製して、その効果を実証した。

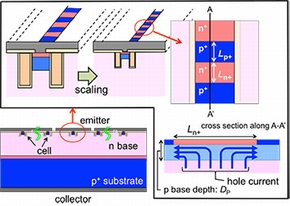

研究チームは、現行のSi-IGBTと同等寸法のデバイスと、新規スケーリングの概念を用いて微細化した新構造のデバイスを作製し、その特性を比較した。作製したSi-IGBTの構造や電流をオン/オフする動作については、従来のデバイスと変わらないという。

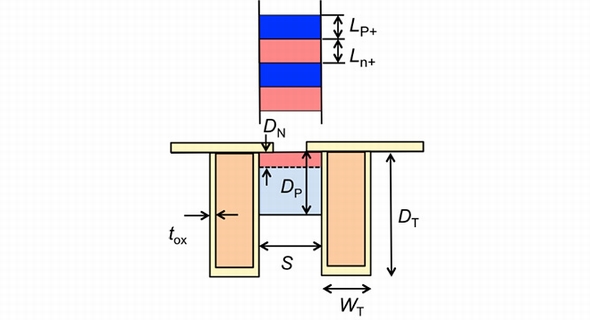

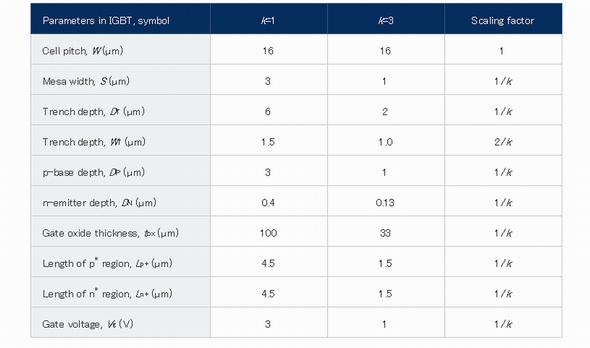

デバイス作製に当たり、寸法の微細化比率をスケーリングファクター1/kで表した。従来デバイスはk=1で、新規デバイスはk=3となる。断面構造において、トレンチゲート周りの寸法は1/kに比例縮小したが、隣接するトレンチゲートまでの距離(W)は一定とした。IGBTの2次元のスケーリングは、CMOS構造のデバイスと異なり、縦横スケーリングが逆の影響、効果になることもあるという。その効果は複雑で、これまでのシミュレーション結果によれば、単位面積当たりのオン電流の密度は増大することが予測されている。今回は、試作したデバイスでこの予測を実証した。

研究グループは、スケーリングで予測されるラッチアップ耐性の劣化に対する対策も行った。試作時にスケーリングパラメーターの一部を見直している。さらに、デバイスの奥行き方向に交互に作られる表面のp形領域とn形領域のピッチ(Lp+およびLn+)も1/kに縮小した。

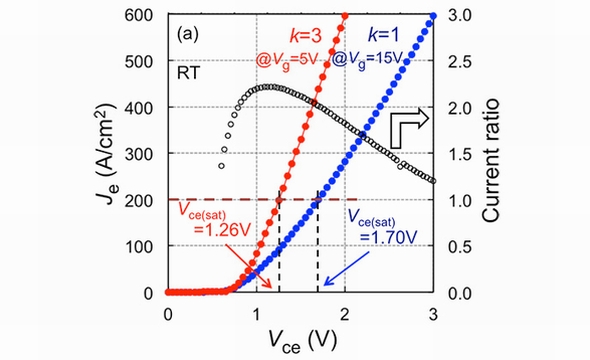

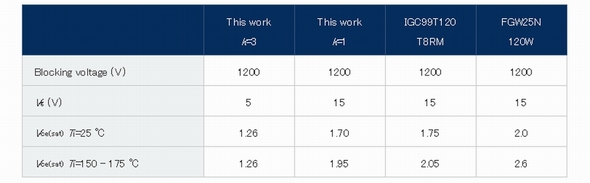

エミッター-コレクター間飽和電圧と呼ぶ、特定のオン電流密度(飽和電流密度)における電圧を測定したところ、k=3スケーリングで1.26Vとなった。従来(k=1)の1.7Vに比べると約70%である。同じエミッター-コレクター間電圧における電流はスケーリングにより約2倍となった。このことは、オン抵抗が半減したことを示す。これらの結果から、スケーリングによりIGBTの低損失と高効率化を実現できることが分かった。

また、IGBTのゲート電圧も従来の15Vに対し、スケーリングによって5Vまで低減させることができた。これによって、IGBTを駆動する回路の消費電力を低減することができ、システムレベルでの高性能化と低コスト化を可能とした。

今回のスケーリングは、IGBTのゲート周りに対して行ったもので、トランジスタ耐圧に関わるnベース層の厚みは変更していない。このため、新構造のIGBTでも耐圧1000~数千Vは維持されるという。

今回の成果は、2016年12月6日に米サンフランシスコで開かれた国際会議「IEDM2016(International Electron Devices Meeting)」で、東工大、東大、九州工業大学、明治大学、産業技術総合研究所、東芝、三菱電機の共同研究として発表された。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -- 雎ク驛�スイ�サ鬮ョ�サ陷牙ケ�スヲ竏オ�ア繧�ソス陷エ�ウ邵コ蜉ア�樣坎蝓滂スク�ャ陷�スヲ騾�ソス縲堤クイ繝セAR陜吩ケ晢ス�セ趣ス」�取ウ梧「帷クコ�ョADC髯ャ�ス陷ゥ竏夲ソス邵コ�ゥ邵コ�ス�ッ�セ陟「諛翫堤クコ髦ェ�狗クコ�ス

- 隴幢スャ霑夲スゥ邵コ�ィ髫募唱�ス邵コ莉」窶イ邵コ�、邵コ荵昶�邵コ�ス�キ�ァ陞ッ蜷カ竊題屁�ス鬨セ�ス陷企宦�ー諠ケ�ス讌「�」�ス陷ゥ竏堋竏ス�シ竏オ�・�ュ邵コ迹夲スェ�ソ鬩墓鱒縲定ア悟干�定脂蛟・��郢ァ荵晢シ�クコ�ィ邵コ�ッ�ス�ス

- [EE Times Japan驍ア�ィ鬮ョ�スホ咯 Intel邵イ竏ス�サ鄙ォ竊千クコ�ス竊醍クコ�」邵コ�ヲ郢ァ蜈キ�シ貅伉ツ髣搾スヲ陟�ソス�定ャ壽㈱��陷�スコ邵コ蟶呻ス狗クコ�ス

- 郢昜サ」ホ。郢晢スシ陷企宦�ー諠ケ�ス阮吶定ア包スィ騾カ�ョ邵コ�ョGaN邵イ竏壹Τ郢晢スッ郢晢スシ郢ァ�「郢晢スウ郢晏干繝ヲ郢ァ�ケ郢晏現�ス髫ア�イ鬯伜セ娯�隴崢鬩包スゥ邵コ�ェ郢ァ�「郢晏干ホ溽ケ晢スシ郢晢ソス

- 隲。�。陞滂スァ邵コ譴ァ謔��包ソス��ケァ蠕鯉ス矩ォア讒ォ諷崎叉鬘費スウ�サ郢晞亂繝」郢晏現ホ。郢晢スシ郢ァ�ッ�ス�スNTN�ス迚呻スク繧�ソス�エ邵イ竏オ諤咎ゥ包スゥ邵コ�ェRF郢晢ソス縺帷ケ晁ご閻ク陟�ソス竊堤クコ�ッ�ス�ス

記事ランキング

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- 暗い夜道でも120m先の歩行者を検知、キヤノンが新SPADセンサー

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- 自律神経から「頑張りすぎ」を可視化、村田製作所

- 自動運転のキーデバイスとなる車載SoC

- キオクシアが攻める「NANDとDRAMのあいだ」 NVIDIAと協業も

- 次はデータセンター 「スマホ以外」にも手を広げるQualcomm

- 商用化から40年を迎えたFPGA、次の主戦場はエッジAI

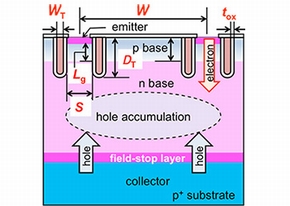

左はSi-IGBTの断面構造、右はSi-IGBTの断面および奥行き方向の構造 出典:東京工業大学

左はSi-IGBTの断面構造、右はSi-IGBTの断面および奥行き方向の構造 出典:東京工業大学 IGBTの3次元方向にわたる各構造寸法の変数 出典:東京工業大学

IGBTの3次元方向にわたる各構造寸法の変数 出典:東京工業大学

試作した2つのIGBTのオン状態におけるエミッター-コレクター間電流-電圧特性 出典:東京工業大学

試作した2つのIGBTのオン状態におけるエミッター-コレクター間電流-電圧特性 出典:東京工業大学

情報漏えいの危険がない、分散ストレージを開発

情報漏えいの危険がない、分散ストレージを開発 蓄電池内部の挙動、原子レベルで解析に成功

蓄電池内部の挙動、原子レベルで解析に成功 希少元素を使わない赤く光る窒化物半導体を発見

希少元素を使わない赤く光る窒化物半導体を発見 高周波圧電共振器の課題を解決する回路

高周波圧電共振器の課題を解決する回路 低閾値電圧の有機Trを実現する化合物を安定合成

低閾値電圧の有機Trを実現する化合物を安定合成 40GHz帯/60GHz帯協調による無線網の実証に成功

40GHz帯/60GHz帯協調による無線網の実証に成功