NVIDIAがエネルギー効率の高い相互接続チップを試作:福田昭のデバイス通信(101) 高性能コンピューティングの相互接続技術(6)(2/2 ページ)

» 2017年01月30日 11時30分 公開

[福田昭,EE Times Japan]

従来技術に比べて消費エネルギーを36%に低減

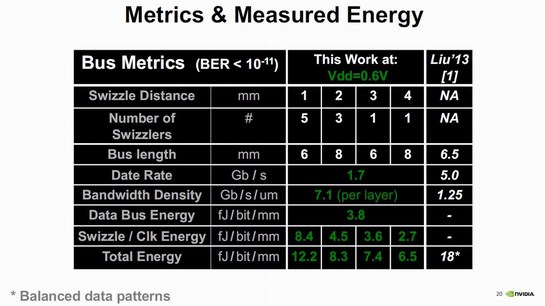

試作したテストチップでは、電源電圧0.6Vのバイアスによって信号を1.7Gビット/秒の速度で伝送した。このときにツイスト回路の間隔の違いと、バスの全長の違いによって伝送ビットおよび単位長当たりの消費エネルギー(fJ/bit/mm)を比較した。

ツイスト回路の数は少ない(ツイスト回路の間隔が長い)方が、消費エネルギーは少なくなった。ただし、ツイスト回路がまったくない場合は中間電位が安定せず、バスとして機能しない。ツイスト回路の挿入は必須であることが分かった。

伝送路の全長が8mm、ツイスト回路を1個だけ挿入したバスが、消費エネルギーが6.5fJ/bit/mmと最も少なかった。この場合、伝送ビットおよび単位長当たりの消費エネルギーは、従来技術と比べて36%と大幅に少なくできた。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

(次の記事を読む)

関連記事

SanDiskが語る、ストレージ・クラス・メモリの信頼性

SanDiskが語る、ストレージ・クラス・メモリの信頼性

SCMとはストレージ・クラス・メモリの略称で、性能的に外部記憶装置(ストレージ)と主記憶(メインメモリ)の間に位置するメモリである。前回は、SanDiskの講演から、SCMの性能とコストに関する比較をメモリセルレベルまで検討した。今回、信頼性について比較した部分をご紹介する。 磁気記憶の高密度化とその課題

磁気記憶の高密度化とその課題

磁気記憶の高密度化手法と、高密度化に伴う本質的な課題を解説する。磁気記憶は、高密度化と低消費電力化で矛盾を抱える――。 ARMから見た7nm CMOS時代のCPU設計(1)

ARMから見た7nm CMOS時代のCPU設計(1)

ARMにとって「IEDM」は非常に重要だ。この会議で議論されるトランジスタ技術が同社のCPUアーキテクチャの行方を左右するからである。ARMは「IEDM 2014」で、CPU設計とデバイス・プロセス技術の関わりを解説する講義を行った。今回から、その内容を複数回にわたってお届けする。 ARMから見た7nm CMOS時代のCPU設計(18)〜壁に突き当たるリソグラフィ技術

ARMから見た7nm CMOS時代のCPU設計(18)〜壁に突き当たるリソグラフィ技術

プロセスルールの微細化において最も困難な課題は、リソグラフィ技術にある。7nm世代の半導体を量産するためのリソグラフィ技術は、いまだに確定していない。現在のところ、解決策としては、従来のArF液浸リソグラフィ技術の改善か、EUV(極端紫外光)リソグラフィ技術の開発が挙げられている。 5Gの加入契約数、2022年には5億5000万件に

5Gの加入契約数、2022年には5億5000万件に

Ericsson(エリクソン)は年に2回、モバイル市場の動向をまとめた「エリクソン・モビリティレポート」を発行している。同レポートの最新版(2016年11月発行)によると、5Gの加入契約数は、2022年には5億5000万件に達する見込みだという。レポートでは5Gの他、V2X(Vehicle to Everything)やセルラーIoT(モノのインターネット)ネットワークについてもカバーしている。 センチ単位で位置検出、日本無線がGNSSチップ

センチ単位で位置検出、日本無線がGNSSチップ

日本無線は、センチメートル級の精度で位置検出が可能な全地球航法衛星システム(GNSS)チップ「JG11」の開発を始めた。自動運転システムなどの用途に向ける。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速