3次元集積化(3D IC)の理想と現実:福田昭のデバイス通信(103) TSMCが解説する最先端パッケージング技術(2)(1/2 ページ)

今回は、なぜシステムを複数のチップに分ける必要があるのかを説明する。後半では、パッケージに求められる目標を達成する“究極のパッケージング技術”として期待されたシリコン貫通ビア(TSV: Through Silicon Via)と、旧世代のパッケージング技術との間に存在する、大きなギャップについて解説したい。

システムを複数のチップに分割する理由

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンダリ最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

本シリーズの初回である前回は、システムのワンチップ化をけん引してきた「ムーアの法則」が動作周波数向上やコスト低減などの点で限界に来ていることと、「ムーアの法則」を拡張するために新世代のパッケージング技術(複数のチップをワンチップに近い水準で1個のパッケージに集積化する技術)が登場してきたことを説明した。

新世代のパッケージング技術の説明に入る前に、複数の半導体チップを1個のパッケージに集積化するのは、どのような場合であるのかをおさらいしておこう。

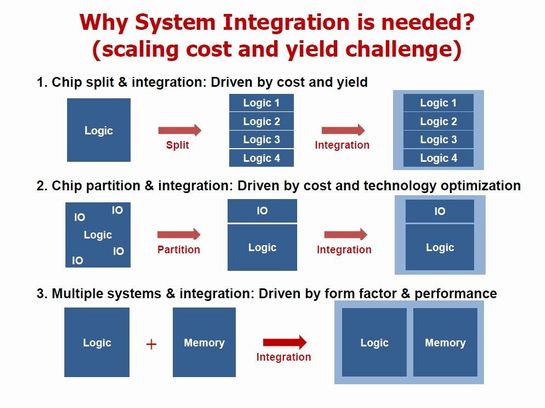

まず、半導体チップが全てロジック回路で構成されている場合である。ロジック回路の規模があまりに大きいと、ワンチップではシリコンダイ面積が大きくなりすぎて、製造コストが上昇するとともに製造歩留まりが高い水準に達しない恐れが出て来る。これを避けるために、複数のチップにロジック回路を分割し、1個のパッケージに集積する。

次は、入出力回路の駆動能力が高く、ロジック回路とは違うプロセス技術で製造する場合である。ワンチップ化した状態をまず考える。すると駆動能力の高い入出力回路が数多く存在し、シリコンダイに分散している状態になる。これは、あまり望ましくない。製造コストが上昇するとともに、プロセスを最適化しにくくなるからだ。そこで入出力回路だけを別のチップに載せ、ロジック回路のチップと分割する。そして1個のパッケージにこれらのチップをまとめる。

3番目は、システムがロジック回路とメモリ回路で構成されている場合である。メモリ回路は、ロジック回路とは異なるプロセス技術で製造していることが多い。駆動能力の高い入出力回路が混在する先の事例と同様に、ワンチップ化せずに、ロジック回路チップとメモリ回路チップに分けることで製造プロセスの最適化を実現できる。後はロジックのチップとメモリのチップを1個のパッケージに集積する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?