モバイル端末向けパッケージング技術「FOWLP」(後編):福田昭のデバイス通信(112) TSMCが解説する最先端パッケージング技術(11)(1/2 ページ)

前回に引き続き、ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」を取り上げる。今回はTSMCなど各社のFOWLPによるパッケージ開発事例を見ていく。

この記事は会員限定です。会員登録すると全てご覧いただけます。

TSMCが開発したFOWLP技術「InFO」

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンダリ最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回すなわち前編では、ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」の製造工程を解説した。後編である今回は、FOWLPによるパッケージの開発事例をご紹介する。

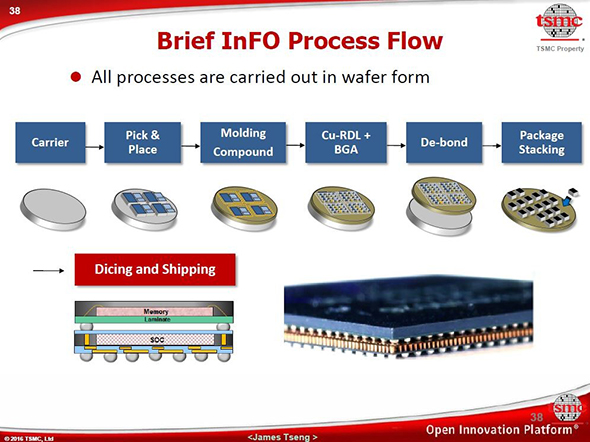

始めはTSMCが開発したFOWLP技術「InFO(Integrated Fan-Out WLP)」である。「InFO」は前編で説明した分類に沿うと、「チップファースト、フェースアップ」の製造工程で作られる。シリコンウエハーと同じ外形寸法のキャリアに、シリコンダイを置いていく。次に、キャリアの片面側全体をモールド樹脂で封止する。それからモールド樹脂の表面を削ってシリコンダイの回路面を露出させ、再構成配置配線層(RDL)を形成し、ハンダボールを載せる。そしてキャリアを外し、個々のパッケージに切断分離すれば、パッケージが完成する。ただし後述するPoPタイプの場合は、切断分離の前にスルーホールとバンプ搭載を実施し、パッケージ封止済みの半導体を載せておく。

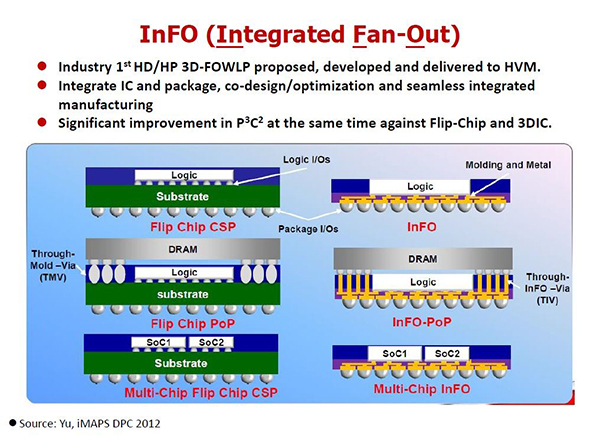

「InFO」の基本仕様は、再配置配線層(RDL)が3層で配線幅/間隔は2μm/2μm、ハンダボールのピッチが0.5mm、パッケージの厚みが0.45mm、パッケージの大きさが15mm角となっている。また「InFO」には、いくつかの派生品が存在する。パッケージ済み半導体デバイスを載せる、PoP(Package on Package)タイプの「InFO-PoP」、複数のシリコンダイを内蔵する「マルチチップInFO」などがある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- Intelの最新AI戦略と製品 「AIが全てのタスクを引き継ぐ時代へ」

- 「VLSIシンポジウム2024」は投稿論文が40%増で激戦に、中国が躍進

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 半導体製造の最先端を独走するTSMCの決算から読み取れること

- 双方向型直流電力変換器、幅広い電圧変動に対応

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ