二酸化ハフニウムを使った強誘電体トランジスタの研究開発(前編):福田昭のストレージ通信(76) 強誘電体メモリの再発見(20)(1/2 ページ)

今回から、「二酸化ハフニウム系強誘電体材料」を使った強誘電体トランジスタ(FeFET)の研究開発状況を報告する。二酸化ハフニウム系強誘電体薄膜は、厚みがわずか7nm程度でも強誘電性を有することが確認されていて、このため、FeFETを微細化できることが大きな特長となっている。

隠されていた二酸化ハフニウムの強誘電体トランジスタ作製

前回では、従来型の強誘電体材料である、「ペロブスカイト系強誘電体材料」を使った強誘電体トランジスタ(FeFET:Ferroelectric FET)の研究開発の状況を説明した。今回からは、新材料である「二酸化ハフニウム系強誘電体材料」を使った強誘電体トランジスタ(FeFET)の研究開発状況をご報告しよう。

本シリーズの第13回「強誘電体メモリの再発見(13)」では、2011年に国際学会でドイツの研究機関Fraunhofer Instituteを中心とする研究グループが、強誘電体の二酸化ハフニウム薄膜を作製したと発表したことが、正式な発見の公表だと述べた。ただしFraunhofer Instituteを中心とする研究グループは、2011年よりも数年ほど前には、強誘電体の二酸化ハフニウム薄膜の作製に成功していた。そして未公表の状態で、研究開発を続けていた。

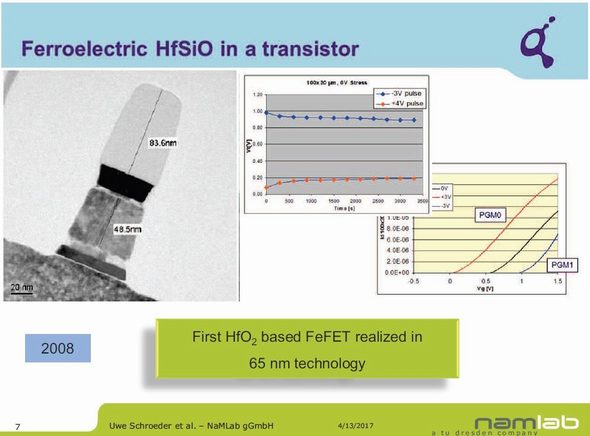

そのことを裏付ける資料がある。2017年5月に開催された「国際メモリワークショップ(IMW)」のショートコースでFraunhofer Instituteを中心とする研究グループは強誘電体メモリに関する技術解説の講演を実施した。その中で、二酸化ハフニウム薄膜をゲート絶縁膜に採用した強誘電体トランジスタの試作結果を示したのだ。

ショートコースで示された講演スライドによると、日付は2008年で、ドイツのDRAMメーカーであるQimonda(2009年に倒産)が65nmの製造技術で試作した。ゲート電極の厚みは83.6nm、二酸化ハフニウム薄膜(シリコン添加)の厚みは48.5nmである。この48.5nmという厚みは、従来型のペロブスカイト系強誘電体ではほぼ、実現不可能な薄さである。言い換えると、この程度にまで薄くできたからこそ、65nmと微細な加工技術が適用できた。ペロブスカイト系では、適用可能な加工技術は130nmにとどまっている。

試作した強誘電体トランジスタは、不揮発性メモリセルとして正常に動作した。初期の試作にもかかわらず、50分程度のデータ保持期間を実現している。ペロブスカイト系の強誘電体トランジスタが当初はデータの保持がうまくいかなかったという厳しい状況と比較すると、雲泥の差がある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速