ISSCC技術講演の初日午後ハイライト(その1)、プロセッサとアナログの最先端技術:福田昭のデバイス通信(126) 2月開催予定のISSCC 2018をプレビュー(2)(1/2 ページ)

「ISSCC 2018」技術講演の初日(2018年2月12日)。午後のハイライトは、最先端のプロセッサおよびアナログ技術の論文発表だ。プロセッサでは、IntelやIBM、AMDが、アナログ技術ではQualcommやMediaTekが、それぞれの研究成果を披露する。

月曜日の午後から技術講演セッションが始まる

前回から、2018年(来年)2月に米国サンフランシスコで開催予定の半導体回路技術に関する国際学会、「ISSCC 2018」の概要をシリーズでお届けしている。今回は、メインイベントである技術講演セッションの初日(2月12日)午後から、ハイライトをご紹介しよう。

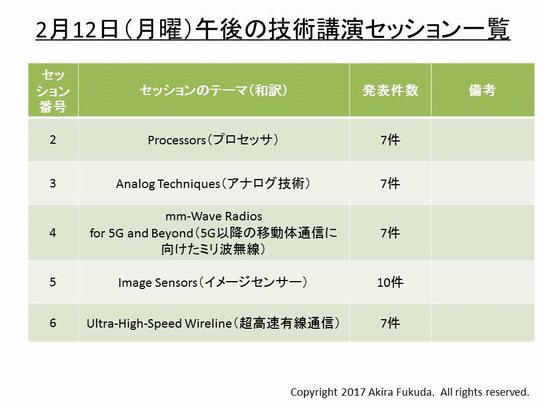

前回でご説明したように、初日の午前はプレナリ講演セッションである。その後、昼食休憩(ランチは提供されない)を挟んで、午後1時30分から一般の技術講演セッションが始まる。セッション番号だと、セッション2からセッション6までの5本の講演セッションが同時並行で進む。セッション名は、プロセッサ(セッション2)、アナログ技術(セッション3)、5G以降の移動体通信に向けたミリ波無線(セッション4)、イメージセンサー(セッション5)、超高速有線通信(セッション6)、である。

Intel、IBM、AMDが最先端のプロセッサ技術を披露

この時間帯の注目すべき講演はまず、セッション2の「プロセッサ」だろう。Intel、IBM、AMDが最先端のプロセッサ技術を披露する。

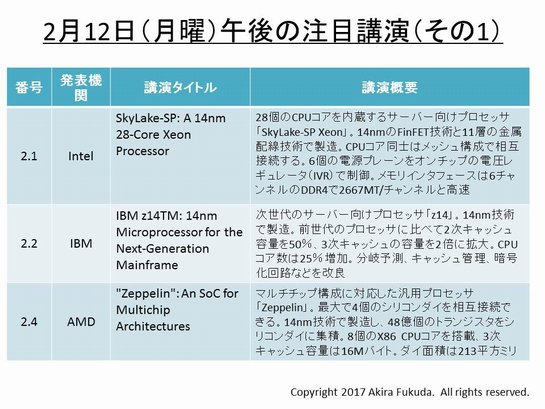

Intelは28個と数多くのx86 CPUコアを内蔵するサーバ用プロセッサ「SkyLake-SP Xeon」の回路技術を発表する(講演番号2.1)。14nm世代のFinFET技術と11層の金属配線技術によって製造する。28個のCPUコアは、メッシュ構成で相互接続される。複数の電圧レギュレーターを内蔵しており、6個の電源プレーンを制御する。メモリインタフェースは6チャンネルのDDR4で、転送速度は2667MT/チャンネルと高速である。

IBMは、次世代のサーバ向けプロセッサ「z14」の回路技術を公表する(講演番号2.2)。14nm技術で製造する。動作周波数は前世代のプロセッサに比べて200MHzほど向上した。また、2次キャッシュの容量を50%、3次キャッシュの容量を2倍に拡大した。CPUコア数は前世代に比べて25%増加している。分岐予測、キャッシュ管理、暗号化回路などを改良した。

AMDは、最新マイクロプロセッサ「Zeppelin」の回路技術を報告する(講演番号2.4)。「Zeppelin」は汎用性が高く、サーバからハイエンドのデスクトップPC、メインストリームのデスクトップPCまでをカバーする。最大で4枚のシリコンダイを相互に接続できる。シリコンダイは14nm技術で製造する。トランジスタ数は48億個である。シリコンダイ面積は213mm2。x86アーキテクチャのCPUコアを8個搭載する。3次キャッシュの容量は16Mバイト。メモリ制御回路と入出力制御回路、サウスブリッジ回路を内蔵する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- わずか3個のLSIでモバイル超音波診断装置を実現、ソシオネクスト

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術