マイコンからHPCまで――RISC-Vが目指す“懐の深さ”:RISC-V Day 2017 Tokyo(2/2 ページ)

シンプルで、スケーラビリティが高い構造

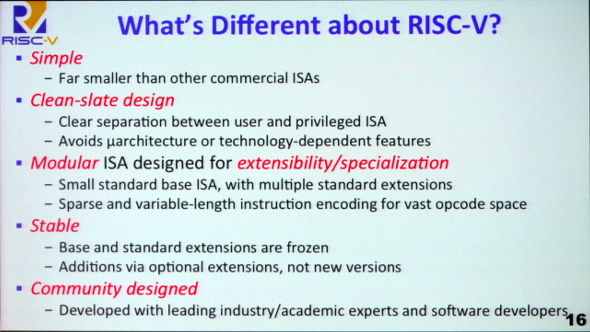

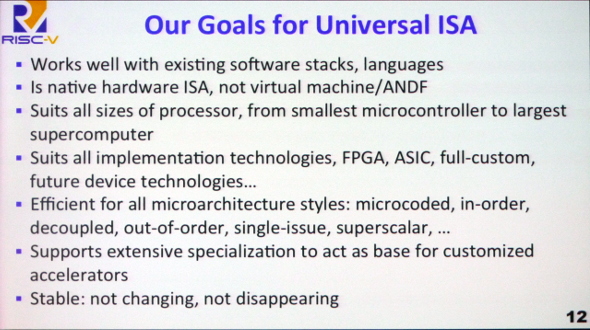

Asanović氏はRISC-Vの特長として、ライセンスがオープンであることだけでなく、シンプルであること、スケーラビリティが高いことを紹介した。

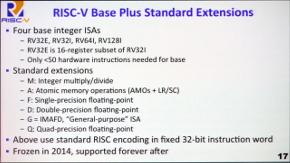

RISC-Vは、小規模でシンプルな4つの整数ISA(RV32E, RV32I, RV64I, RV128I)を用意し、機能追加は標準拡張ISA(整数の乗除算を提供するM, アトミックなメモリアクセスを提供するA, 単精度浮動小数点演算を提供するF, 倍精度浮動小数点演算を提供するD, 4倍精度浮動小数点演算を提供するQ、組み込み用途向けに命令長を16ビットに圧縮したCなど)で実現するモジュラー構造を取る。この整数ISAと標準拡張ISAは、2014年に仕様が凍結し永久にサポートされるという。

これにより、RISC-Vを用いたチップの設計者は、必要な機能を提供するISAのみを実装できるというメリットがある。また、可変長命令をサポートした空のオペコードも用意されているため、第三者による拡張命令セットの実装も可能だ。

このような特長を持ちつつ、現在用いられているプログラミング言語への幅広い対応や、マイコンからHPC(High Performance Computing)まで単一のISAでサポートできること、FPGAやASIC、フルカスタムといった実装方法に全て適合することを目標として、RISC-Vの開発を進めてきたという。

Asanović氏は講演の終盤で、インドにおいて国家標準ISAとしてRISC-Vへの投資が進んでいることや、NVIDIAが将来のGPUにRISC-Vを採用するとアナウンスしたことにも触れており、エコシステムが広がりつつあることを強調する。また、コンピュータ技術に関する教本として名高いJohn L.Hennessy氏とDavid A.Patterson氏の共著「Computer Architecture」第6版にも、RISC-Vが命令セットの解説に採用されたことを紹介した。

RISC-V Day 2017 Tokyoでは、RISC-Vを採用し4096コアを搭載したHPC用プロセッサを開発するEsperanto社で技術メンバーを務める笠原栄二氏も講演をしており、こちらも別途紹介する予定だ。

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- Xiaomi 15S Proを分解、10年かけて磨き続けた半導体開発力

- 半導体のネガティブイメージ解消へ、ソニーやキオクシアら国内大手が集結

- 中国半導体装置展示会「CSEAC」レポート 中工程シフトと“露光回避”の実態

- 「充電5分で520km走行」を巡る疑問、 中国CATLの車載バッテリー発表を考察

- 創刊前の20年間(1985年~2005年)で最も驚いたこと:「高輝度青色発光ダイオード」(前編)

- 「鉄とマンガン」が半導体の微細化を進化させる?

- 「CEATEC 2025」ことしも10万人超えへ 吉村知事が万博語るセッションも

- TO-247より省面積、ロームの新SiCパワーモジュール

- STがパネルレベルパッケージの試作ライン新設へ 6000万ドル投じ

- SiFiveの新RISC-VコアはAI特化 メモリ管理の革新で性能向上

関心高まるRISC-V、Armやx86の代替となり得るか

関心高まるRISC-V、Armやx86の代替となり得るか RISC-Vベースチップ手掛ける新興企業が資金調達

RISC-Vベースチップ手掛ける新興企業が資金調達 Microsemi、FPGA向けのRISC-V IPコアを提供へ

Microsemi、FPGA向けのRISC-V IPコアを提供へ ムーアの法則の終息でIDMの時代に“逆戻り”か?

ムーアの法則の終息でIDMの時代に“逆戻り”か? MIPSコンピュータをめぐる栄枯盛衰

MIPSコンピュータをめぐる栄枯盛衰 Imaginationが身売りへ、Appleの取引停止宣告余波

Imaginationが身売りへ、Appleの取引停止宣告余波