ISSCC技術講演の2日目午前ハイライト(その2)、GPS不要の超小型ナビ、16Gビット高速大容量DRAMなど:福田昭のデバイス通信(129) 2月開催予定のISSCC 2018をプレビュー(5)(2/2 ページ)

靴のかかとに組み込む超小型ナビゲーションシステム

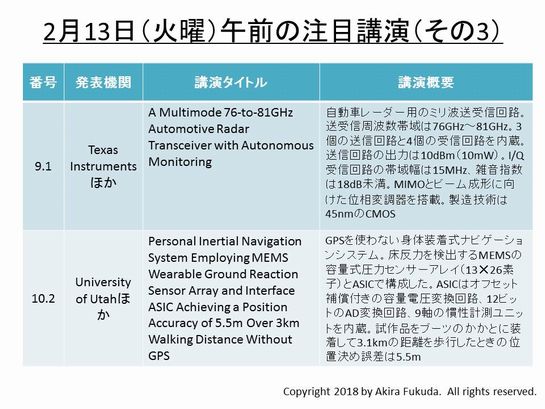

セッション10の「センサーシステム」では、身体に装着可能であり、GPS信号を受信困難な環境で使える超小型ナビゲーションシステムの発表が非常に面白そうだ。

University of UtahとUniversity of California at Berkeley、Ozyegin University、Case Western Reserve Universityの共同研究チームは、GPS信号を受信困難な環境で使え、身体に装着できるほど小さな慣性式ナビゲーションシステムを発表する(講演番号10.2)。靴のかかとに組み込むことを想定した。人間が歩く際に靴が床を蹴るときの反力(床反力)を圧力センサーによって検出し、移動方向と移動距離を算出する。圧力センサーはMEMS技術による容量式センサーのアレイである。素子数は13×26素子。このセンサーアレイとASICを組み合わせてシステムを構成する。

ASICは容量を電圧に変換する回路(プログラム可能なオフセット補償機能付き)、12ビットのアナログデジタル(AD)変換回路、9軸の慣性計測ユニット(IMU)を内蔵する。システムの試作品をブーツのかかとに装着して3100mの距離を歩行したところ、位置の計測誤差は5.5mにとどまった。

入出力ピン当たり5Gビット/秒の超高速モバイル16GビットDRAM

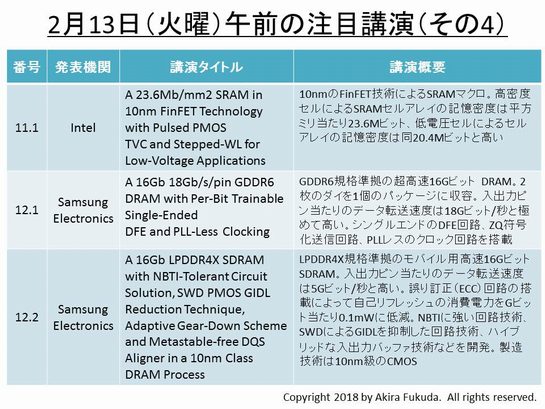

セッション11の「SRAM」はハーフセッションで、発表件数は3件とあまり多くない。このセッションでは、Intelが10nmと微細なFinFET技術を駆使した高密度SRAM技術を発表する(講演番号11.1)。高密度タイプのメモリセルの面積は0.0312μm2と小さい。SRAMセルアレイの密度は23.6Mビット/mm2に達する。低電圧タイプのメモリセルの面積は0.0367μm2、セルアレイの密度は20.4Mビット/秒である。電源電圧を下げる回路技術の内容を講演する予定だ。

セッション12の「DRAM」もハーフセッションで、こちらは5件の発表を予定している。このセッションではSamsung Electronicsが16Gビットと大容量の高速DRAMを報告する。報告は2件ある。

1件はグラフィックスDRAM規格のGDDR6に準拠した16GビットDRAMの発表である(講演番号12.1)。2枚のシリコンダイを1個のパッケージに収容した。入出力ピン当たりのデータ転送速度は18Gビット/秒に達する。データ転送速度を向上するため、シングルエンドのDFE(Decision Feedback Equalizer)回路、ZQ符号化送信回路、PLLレスのクロック回路を搭載した。

もう1件はモバイルDRAM規格のLPDDR4Xに準拠した16GビットSDRAMの発表である(講演番号12.2)。入出力ピン当たりのデータ転送速度は5Gビット/秒と高い。誤り訂正(ECC)回路の搭載によって自己リフレッシュの消費電力をGビット当たりでわずか0.1mWに低減した。NBTI(Negative Bias Temperature Instability)に強い回路技術、サブワード線ドライバ(SWD: Sub-Word line Driver)によるGIDL(Gate Induced Drain Leakage)の発生を低減する回路技術、ハイブリッドな入出力バッファ技術などを報告する。製造技術は10nm級と微細なCMOS DRAMプロセスである。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ISSCC(国際固体回路会議)とは何か

ISSCC(国際固体回路会議)とは何か

毎年2月に開催される、半導体チップの回路技術とシステム技術に関する国際学会「ISSCC(国際固体回路会議)」。えり抜きの論文が発表される重要なイベントだ。今回から始まる本シリーズでは、開催を2カ月後に控えたISSCCについて、概要と注目論文を紹介する。 Intelの高性能・高密度パッケージング技術「EMIB」の概要

Intelの高性能・高密度パッケージング技術「EMIB」の概要

今回は、Intelが開発した2.nD(2.n次元)のパッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」を解説する。EMIBではシリコンインターポーザの代わりに「シリコンブリッジ」を使う。その利点とは何だろうか。 「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術

「SEMICON West 2016」、Synopsysが予測する5nm世代のトランジスタ技術

Synopsysの講演では、5nm世代のトランジスタのシミュレーション評価結果が報告された。この結果からはFinFETの限界が明確に見えてくる。5nm世代に限らず、プロセスの微細化が進むと特に深刻になってくるのが、トランジスタ性能のばらつきだ。 半導体プロセスの先導役はPCからモバイルに、2017年は“真の転換点”だった

半導体プロセスの先導役はPCからモバイルに、2017年は“真の転換点”だった

2017年は、プロセッサに適用する最先端製造プロセスの導入において、モバイルがPCを先行した。その意味で、2017年は半導体業界にとって“真の転換点”ともいえる年となりそうだ。今、PC向けとモバイル向けのプロセッサは、製造プロセスについて2つの異なる方向性が見えている。 半導体メモリの専門学会「国際メモリワークショップ(IMW)」が日本で開催へ

半導体メモリの専門学会「国際メモリワークショップ(IMW)」が日本で開催へ

2008〜2017年まで主に米国で開催されてきた「国際メモリワークショップ(IMW)」が、2018年は日本の京都で開催される。今回はIMWの概要を紹介しよう。 反強誘電体とは何か

反強誘電体とは何か

強誘電体の新材料である二酸化ハフニウムは、実は条件次第では「反強誘電体(Antiferroelectrics)」になる。今回から、この反強誘電体を不揮発性メモリに応用する研究について解説していこう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」