埋め込みフラッシュIP大手ベンダーSSTのメモリ技術:福田昭のストレージ通信(95) STが語る車載用埋め込み不揮発性メモリ(8)(2/2 ページ)

» 2018年03月27日 09時30分 公開

[福田昭,EE Times Japan]

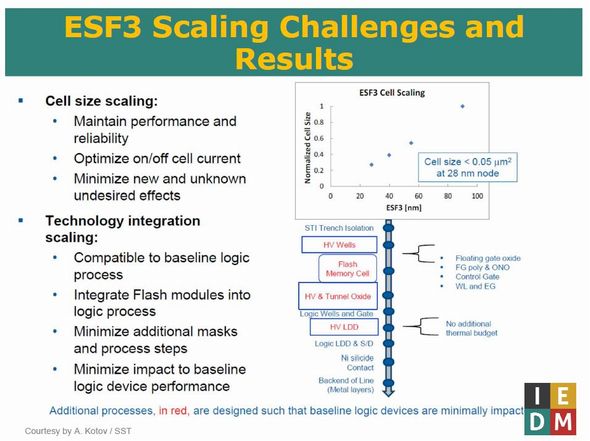

最新世代の「ESF3」技術で28nm以下の微細化を目指す

最新世代の「ESF3」では、結合ゲート(CG: Coupling Gate)の導入によって微細化をさらに押し進めた。120nm、90nm、65/55nm、45/40nm、28nmの製造技術で使われている。10年を超える量産実績がある。

ESF3の導入によってメモリセル面積はかなり小さくなった。90nm技術のメモリセル面積を「1」とすると、28nm技術のメモリセル面積は、「0.3」になる。具体的には、0.05μm2以下を実現できているとする。

製造プロセスは、CMOSロジックのプロセスに高電圧用のウエル形成とセルトランジスタ形成、高電圧対応絶縁膜形成とトンネル絶縁膜形成などを追加したものである。追加するプロセスは、モジュール化されている。

フラッシュメモリの微細化で問題となるのは、セルトランジスタが蓄積する電荷のばらつきである。SSTのSuperFlash技術の場合、ESF3の28nm技術でも1000個を超える電子をセルトランジスタに蓄積できている。電荷のばらつきが信頼性に与える影響は極めて小さい。このため、28nm以下に微細化する余地がある。

ESFの技術世代とセルトランジスタが蓄積する電子数の推移。縦軸が電子の数、横軸が微細加工寸法。ESF3技術では、微細化しても電子の数がそれほど減らないことが分かる。出典:STMicroelectronics(クリックで拡大)

ESFの技術世代とセルトランジスタが蓄積する電子数の推移。縦軸が電子の数、横軸が微細加工寸法。ESF3技術では、微細化しても電子の数がそれほど減らないことが分かる。出典:STMicroelectronics(クリックで拡大)(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

従来型材料を使った強誘電体トランジスタの研究開発(前編)

従来型材料を使った強誘電体トランジスタの研究開発(前編)

強誘電体トランジスタ(FeFET)の原理は比較的単純だが、トランジスタの設計と製造は極めて難しい。1990年代前半から開発が続く中、約30日というデータ保持期間を強誘電体トランジスタで初めて実現したのは、日本の産業技術総合研究所(産総研)だった。 車載電装システム市場、2025年に35兆円規模へ

車載電装システム市場、2025年に35兆円規模へ

車載電装システムの世界市場は、2017年見込みの21兆円超に対し、2025年には35兆円規模となる見通しだ。電動化や自動運転など、地球環境あるいは安全にかかわるシステムの需要が拡大する。 STMicroelectronicsの埋め込みフラッシュメモリ技術(前編)

STMicroelectronicsの埋め込みフラッシュメモリ技術(前編)

今回は、開発各社の埋め込みフラッシュメモリ技術を前後編にわたって紹介する。前編では、STMicroelectronicsが製品化している、1トランジスタのNORフラッシュ(1T NOR eFlash)技術を取り上げる。 車載用の埋め込みフラッシュメモリ技術

車載用の埋め込みフラッシュメモリ技術

今回は、大容量、具体的には車載用の埋め込み不揮発性メモリ技術を取り上げる。車載用の不揮発性メモリ技術は、1トランジスタのNORフラッシュ(1T NOR Flash)技術と、スプリットゲートフラッシュ技術に大別される。 半導体前工程の設備投資額、2019年まで4年連続成長へ

半導体前工程の設備投資額、2019年まで4年連続成長へ

半導体前工程ファブに対する設備投資額は、4年連続で成長する見通しだ。中国における新工場の建設ラッシュが需要を押し上げる。2019年には投資額で韓国を抜き、中国が世界最大の地域になるとSEMIは予測する。 Samsungが設備投資費を倍増、中国には痛手か

Samsungが設備投資費を倍増、中国には痛手か

DRAMの強いニーズを受け、Samsung Electronicsは半導体設備投資費を拡大する。2016年の113億米ドルから倍増し、2017年は260億米ドルとなる見込みだ。メモリに力を入れる中国にとっては、Samsungとの差がさらに大きく開く可能性もある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- わずか3個のLSIでモバイル超音波診断装置を実現、ソシオネクスト

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」