光変調器を駆動する高速CMOS回路の試作事例:福田昭のデバイス通信(164) imecが語る最新のシリコンフォトニクス技術(24)(1/2 ページ)

今回は、光変調器を高速で駆動する電気回路、すなわちシリコンCMOSのドライバ回路を試作した事例を説明する。

リング変調器を高速で駆動するCMOS回路

半導体デバイス技術に関する国際会議「IEDM」では、カンファレンスの前々日に「チュートリアル(Tutorial)」と呼ぶ技術セミナーを開催している。2017年12月に開催されたIEDMでは、6件のチュートリアルが開催された。

その中から、シリコンフォトニクスに関する講座「Silicon Photonics for Next-Generation Optical Interconnects(次世代光接続に向けたシリコンフォトニクス)」が興味深かったので、その概要をシリーズでお届けしている。講演者は、ベルギーの研究開発機関imecのJoris Van Campenhout氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前々回と前回は、16チャンネルで896Gビット/秒(bps)と極めて広い帯域幅の光伝送を実現した超高速光送受信モジュールの試作例を前後編でご紹介した。今回は、光変調器を高速で駆動する電気回路、すなわちシリコンCMOSのドライバ回路を試作した事例をご説明する。

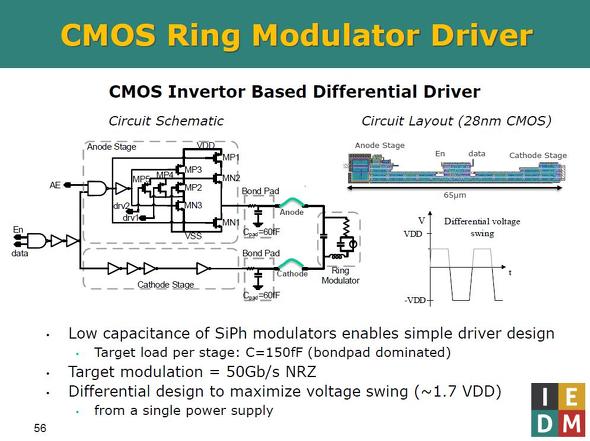

講演で紹介したのは、リング共振器を使った光変調器「リング変調器」を駆動するCMOS回路である。シリコンフォトニクスで作製するリング変調器には入力容量(CMOSドライバ回路の負荷容量)が小さいという特長があり、CMOS回路の構成を簡素にできる。

基本的な考え方は、CMOSインバータを基本とする差動方式によってリング変調器をドライブすることだ。シングルエンド方式ではなく差動(ディファレンシャル)方式を採用するのは、ドライブする信号の振幅を大きくするためである。電源電圧(VDD)の1.7倍に相当する振幅を得られる。電源は単一電圧である。

具体的には、入力データを2つに分割してアノード回路(アノード段)とカソード回路(カソード段)にそれぞれ送り、差動方式で駆動する。アノード段は増幅回路、カソード段はインバータ回路である。

試作したCMOSドライバ回路のシリコンダイとリング変調器ダイとの接続には、ワイヤボンディングを使う。ワイヤボンディングのパッドによる静電容量を含めて負荷容量の合計値は150fFを想定した。ドライブする変調器の速度は、NRZ符号で56Gbpsを目標仕様とした。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- センサーで微細プロセス、ロジックも12nm導入へ ソニーのイメージセンサー戦略

- 自動運転のキーデバイスとなる車載SoC

- キオクシアが攻める「NANDとDRAMのあいだ」 NVIDIAと協業も

- 次はデータセンター 「スマホ以外」にも手を広げるQualcomm

- AMDがAI新興Untether AIのエンジニアチーム「だけ」買収

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ