Arm MLプロセッサ、明らかになったその中身:モバイル機器でのエッジAI向け(1/5 ページ)

2018年8月に開催された「Hot Chips 30」では、Armの「ML Processor(MLプロセッサ)」の中身が明らかになった。その詳細を解説する。

2018年3月に、「ArmのAI戦略、見え始めたシナリオ」という記事を書かせていただいたが、この時には内部構造が一切明らかにされなかったArm MLプロセッサの詳細が、この8月に開催された「Hot Chips 30」でArmのIan Bratt氏(Distinguished Engineer and Director of Technology, ML)によって説明された。そこで、この中身をご紹介したいと思う。

Mobile SoCのアクセラレータ的に利用

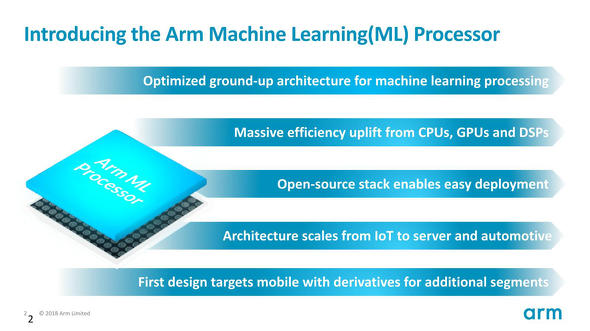

Arm MLプロセッサの基本的な特徴が図1である。

図1 とはいえ、"with derivatives for additional segments"とあるように、別のプロセッサ(例えばCortex-Mシリーズ)と組み合わせる事も可能なように配慮はされている模様 出典:Arm(クリックで拡大)

図1 とはいえ、"with derivatives for additional segments"とあるように、別のプロセッサ(例えばCortex-Mシリーズ)と組み合わせる事も可能なように配慮はされている模様 出典:Arm(クリックで拡大)ポイントとなるのは多分、最後の"First design targers mobile"である。つまりArmはMLプロセッサを単体のIP(Intellectual Property)として提供するというよりは、Mobile SoCのアクセラレータ的に利用することを念頭に置いているということだ。実はこのマーケット、例えばQualcommはDSPベースのNPE(Neural Processing Engine)を、HiSiliconはKirin SoCにNPU(Neural Processing Unit)をそれぞれアクセラレータとして搭載しており、これの代替を狙っているのが明白である。

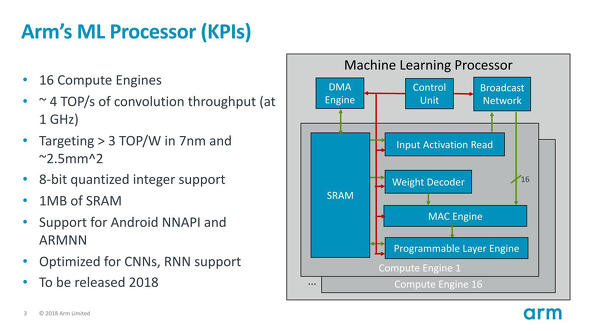

まずラフな内部構成が図2である。

最大16個のCompute Engineが集積され、この外側にDMA EngineとBroadcast Networkおよび、両者(とCompute Engine)を制御するControl Unitが用意されるという構成である。外部I/Fに関しては後で。恐らく、AXI程度の用意はDMA EngineないしControl Unitの中にあるのではないかという気がする。

さて設計目標はConvolution(畳み込み演算)で4TOP/sec@1GHzとあるので、Compute Engine1個当たり256Ops/CycleのConvolutionが実行できる計算になる。ターゲットが7nmで3TOP/Wとあるのは意外に控えめな感じがする。それと7nmプロセスで2.5mm2というエリアサイズはかなり大きめに感じるが、恐らくこれはCompute Engine当たり1MB(つまり16Compute Engineで合計16MB)という巨大なSRAMのためだろう。

扱うデータは8bit Integer(整数)で、これはまぁ妥当なところだろう。FPGAであれば1bitとか2bitにデータサイズを減らしても、それに合わせて内部構成を最適化することができるから、その分並列度を上げやすいが、汎用プロセッサでこれは難しい(無理に1~2bit幅のデータ型を用意するとなると、むしろ回路構成が複雑になりすぎて無駄が多くなる)。むしろ8bit幅のまま、4TOP/secをいかに実現するかに専念した方が効果的という判断であろう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents 2

- PR -記事ランキング

- 「AppleがSamsungから半導体調達」報道、ソニーの反応は

- 「GaNのコストは5年以内にSi並みに」 ロームの勝ち筋は

- 世界半導体製造装置市場、2026年は過去最高に

- タイワン・セミコンダクターがSiCパワー半導体市場に参入、その狙いは

- アオイ電子がシャープ三重第2工場も買収、先端半導体パッケージ強化

- 「われわれのDNAは製造業」 半導体用材料開発を加速する田中貴金属

- Teslaとの契約はSamsungを回復に導くのか

- 2024年のイメージセンサー市場もソニーがトップ、高まる中国の存在感

- 半導体微細化の立役者! フォトマスクの進化の歴史

- 93%減益のソシオネクスト、車載の新規量産で2Qから売上高増へ