ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?:メモリ関連の論文も豊富(2/2 ページ)

5GではIntelとSamsungが火花を散らす

高速ネットワークの分野では、SamsungとIntelがそれぞれ、5GとLTEの両方に対応するトランシーバーについて発表する予定だ。

Samsungは、14nmプロセスを適用した、面積が38.4mm2のチップについて詳細を明らかにする。2G/3G/LTEに対応し、スタンドアロン(SA)/ノンスタンドアロン(NSA)の5Gをサポート可能だという。14個のレシーバーと2つの伝送パスを使用して、最大で下り3.15Gビット/秒(bps)、上り1.27Gbpsの通信速度を実現する。

Samsungは関連論文の中で、6GHz帯以下を使う5Gネットワークに向けたモジュレーターについて発表するという。エンベロープトラッキング向けに100MHz帯域幅をサポートし、効率は88%を実現する。また、立ち上がり90ナノ秒/V、立ち下がり110ナノ秒/Vの能力を持つミリ波トランシーバー向けの電力管理ICについても説明する予定だ。

これらは、Samsungの5Gチップセット「Exynos Modem 5100」の一部で、6GHz未満とミリ波の両方のネットワークをサポートするという。同社はこのExynos Modem 5100を、ISSCCのデモイベントにおいて披露する予定だ。このことからも、Samsungが、5G市場のリーダーであるQualcommに対し、脅威的なライバルになることを目指していると分かる。

SamsungだけでなくIntelも、6GHz帯以下に対応するゼロIF(ZIF)と、ミリ波帯向けの10.556GHz IFに向けた、28nmプロセス適用の4G/5Gトランシーバーを発表する予定だ。MIMO向けにM-PHY HS-Gear3インタフェースを搭載し、キャリアアグリゲーションで最大800MHzの帯域幅をサポートする。これは、Intelが2018年11月初めに発表した、5Gチップセットの一部である。

有線ネットワークも、その勢いを拡大している。HuaweiとeSilicon、MediaTek、IBMは、7nmプロセス適用デバイスを発表する予定だ。最大データ転送速度が128Gbpsで、通常はPAM-4変調を使用する。このPAM-4変調については数年前、実用化が可能かどうかをめぐり、活発な討論が繰り広げられた。

東芝は、データ時代のストレージに対するニーズに対応すべく、4ビット/セル(QLC)技術を適用した、1.33Tビットの3D NANDフラッシュチップを披露する。96層積層プロセスを用いる。記録密度は8.5Gビット/mm2となっている。

そのライバルであるWestern Digitalは、128層を持つ512Gビットの3ビット/セルチップを発表する。メモリアレイの下に制御回路を配置し、書き込みスループットは132Mバイト/秒を実現する。

Samsungは、12Gビット/秒を提供可能な、512Gビットの3ビット/セルチップを披露する。ワード線/ビット線の設定時間を削減することにより、読み書き性能の向上を実現するという。

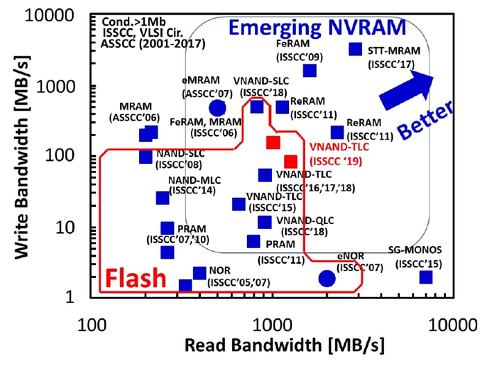

組み込みメモリ分野では、Intelが、同社の22nm FinFETプロセスを適用した最先端のReRAM/MRAM(磁気抵抗メモリ)のデモを披露する。

自動運転車向けのレーダーでは、MediaTekが、パッケージサイズが16×25mmの79GHz帯対応トランシーバーについて発表する。Intelは、同社の22nmプロセスを使った、71G〜76GHz帯対応の64素子フェーズドアレイトランシーバーについて説明する。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

ISSCC(国際固体回路会議)とは何か

ISSCC(国際固体回路会議)とは何か

毎年2月に開催される、半導体チップの回路技術とシステム技術に関する国際学会「ISSCC(国際固体回路会議)」。えり抜きの論文が発表される重要なイベントだ。今回から始まる本シリーズでは、開催を2カ月後に控えたISSCCについて、概要と注目論文を紹介する。 AIプロセッサを開発した東芝メモリの狙い

AIプロセッサを開発した東芝メモリの狙い

東芝メモリは2018年11月6日、ディープラーニング専用のプロセッサを開発したと発表した。今回同社が開発したのは、推論向けの技術。アルゴリズムとハードウェアの協調設計により、従来の方法に比べて認識精度をほとんど劣化させずに演算量を削減し、推論の高速化と低消費電力化を図ることに成功した。 大幅に消費電力を低減したFRAMを発表

大幅に消費電力を低減したFRAMを発表

Cypress Semiconductor(サイプレス セミコンダクタ)は2018年11月14日に開幕した展示会「ET&IoT Technology 2018」(会場:パシフィコ横浜/会期:2018年11月16日まで)で、超低消費電力を特長にしたFRAM(強誘電体メモリ)の新製品「Excelon LP F-RAM」を発表した。 環境発電で“欠けていたピース”埋める、ルネサスのSOTB

環境発電で“欠けていたピース”埋める、ルネサスのSOTB

ルネサス エレクトロニクスはドイツ・ミュンヘンで開催された「electronica 2018」(2018年11月13〜16日)で、エナジーハーベスト(環境発電)で得たエネルギーで駆動できる組み込みコントローラー「R7F0E」を発表した。核となるのはルネサス独自のプロセス技術「SOTB(Silicon On Thin Buried Oxide)」である。 AMD、7nmチップでIntelとNVIDIAに真っ向勝負

AMD、7nmチップでIntelとNVIDIAに真っ向勝負

AMDは、利益が見込めるデータセンターをターゲットとする、7nmプロセスのCPUとGPUを発表した。Intelの14nmプロセス適用プロセッサ「Xeon」とNVIDIAの12nmプロセス適用「Volta」に匹敵する性能を実現するとしている。 Samsung、EUV適用7nmチップ開発を加速

Samsung、EUV適用7nmチップ開発を加速

ファウンドリーの間で現在、EUV(極端紫外線)リソグラフィを使用した業界初となる半導体チップを実現すべく、競争が繰り広げられている。Samsung Electronics(以下、Samsung)は、「EUVリソグラフィを適用した複数の7nmプロセスチップをテープアウトした」と発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速