2019年も大注目! 出そろい始めた「エッジAIプロセッサ」の現在地とこれから:この10年で起こったこと、次の10年で起こること(31)(2/3 ページ)

現行のAIアクセラレーターの現在地

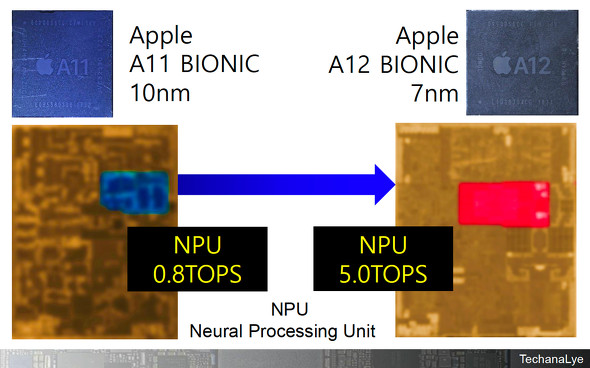

図2はAIアクセラレーターを搭載するAppleの2017年プロセッサ「A11 BIONIC」と2018年の「A12 BIONIC」のチップ全体写真の内、AIアクセラレーター部を着色したものだ。前者は10nm、後者は7nmで製造されている。集積密度は10nmから7nmへの微細化によって1.688倍高まっている(チップサイズ測長とApple発表のトランジスタ数から算出)。

A11から顔認証用に新たに搭載されたNPUは、A12ではおおよそ6〜7倍の性能向上を果たしている。Appleの公式Webサイトにも本値は公表されている。なお、1TOPSとは1秒間に1兆回の演算を行うという意味である。A12のNPUは5TOPSなので、NPUを構成する8ビットの小さな演算器を1秒間に5兆回、回すわけだ。ドットプロジェクターと赤外線カメラから取得した画像データをNPUで機械学習して顔画像をIDとして活用しているのだ。チップサイズとIPの大きさをそれぞれ測長し、計算することで1TOPSに必要な面積を求めることができる。

機能的にコンパクトで高い性能

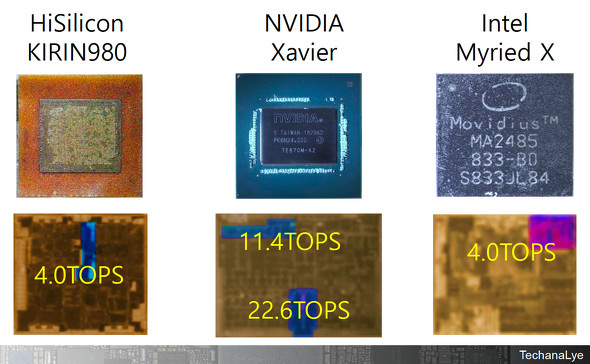

図3は、2018年に発売されたAIアクセラーターを持つプロセッサをテカナリエで解析した結果の極一部である。弊社ではほとんどのプロセッサを入手し同様の解析や算出を行っている(実際には鮮明な写真でレポートを提供している)。冒頭で述べたようにQualcommやMediaTekのプロセッサや車載系プロセッサなども解析済だ。

図3左は中国HUAWEI傘下の半導体メーカーHiSiliconの最新プロセッサ「KIRIN980」、中央はNVIDIAの新プラットフォーム「Xavier」、右はIntelの空間認識アクセラレータープロセッサ「Movidius Myriad X」のチップ開封(サイズ測長および、プロセス判定済)とAIアクセラレーター部を着色した様子である。AIアクセラレーターはチップのおおよそ数%から10%程度の面積に収まっている。

チップは工業製品なので小さいほどコストがかからない(面積が大きいとコストは増える/ウエハーからのチップ取得数が決まる)。小さな面積の中に高い性能を詰め込むためには、IPの方式設計から開発を行わねばならない(ルネサスDRPやNSITEXEのDFPの価値はここにある! 新しいIPを取り組むことは価値の創生だ)。機能的にコンパクトで高い性能が出せればより良いわけだ。一方でプロセステクノロジーを進化させ、小型化させることも性能の向上と電力の削減には大きな効果がある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- わずか3個のLSIでモバイル超音波診断装置を実現、ソシオネクスト

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」