東芝 低消費のBLE向け無線受信アーキテクチャ:デジタル型周波数シンセ採用、ADC不要に

東芝は、Bluetooth Low Energy(BLE)向けの無線受信アーキテクチャを開発した。従来のアナログ回路を用いた無線受信機に比べて、消費電力を約10%も削減することが可能となる。

東芝は2016年2月、Bluetooth Low Energy(BLE)向けの無線受信アーキテクチャを開発したと発表した。従来のアナログ回路を用いた無線受信機に比べて、消費電力を約10%も削減できる。このため、バッテリー駆動の無線機器を、より長い時間使うことが可能になるという。

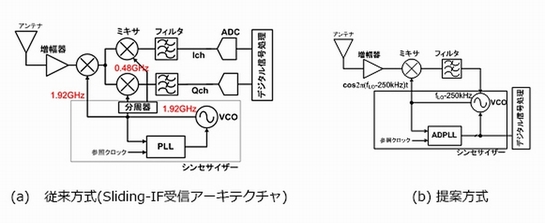

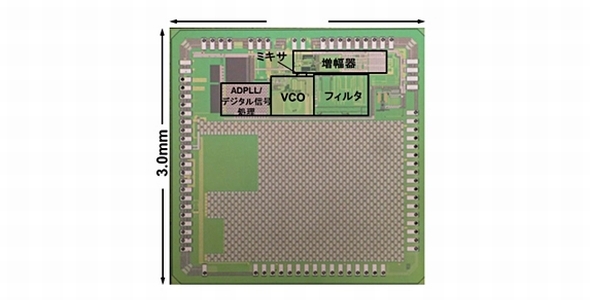

新たに開発したBLE向け無線受信アーキテクチャは、大きく2つの特長を持つ。これまでは同相成分と直交成分の2系統のアナログ信号処理回路を用いてデータ復調処理を行ってきた。今回は、周波数シンセサイザーの設定周波数を工夫することにより、この処理を同相成分の1系統のみで実現することができるという。

もう1つは、受信機にデジタル型周波数シンセサイザーを用いたことで、復調処理用のA-Dコンバーターを不要とした。周波数シンセサイザーとしての外乱(雑音)除去機能を活用して、デジタル型周波数シンセサイザーのみで受信信号を復調する機能を実現している。

新たな受信アーキテクチャを開発/採用したことで、信号を復調するための回路ブロックを削減することができる。A-Dコンバーターも不要とするなど、使用する部品点数の削減が可能となった。これらの工夫により、従来のアナログ回路を用いた場合に比べて、消費電力を低減することができるという。開発した技術は、ウェアラブルデバイスやインフラ監視用センサーネットワークシステムへの応用を視野に入れ、早期実用化を目指していく方針だ。

開発した技術の詳細は、米国サンフランシスコで開催される半導体集積回路技術の国際会議「ISSCC(IEEE International Solid-State Circuits Conference) 2016」(2016年1月31日〜2月4日)で、現地時間2月3日に発表する。

関連記事

STT-MRAMでSRAM比1/10以下の消費電力を達成

STT-MRAMでSRAM比1/10以下の消費電力を達成

東芝と東京大学は2016年2月1日、「あらゆる種類のメモリと比べ世界最高の電力性能」というMRAMを開発したと発表した。 東芝、3D NAND製造用に四日市工場の敷地を拡張

東芝、3D NAND製造用に四日市工場の敷地を拡張

東芝は、3次元NAND型フラッシュメモリの製造に向け、四日市工場の敷地を拡張すべく、同工場の隣接地を取得すると発表した。 企業論文の採択率回復、日本は2位に、ISSCC概要

企業論文の採択率回復、日本は2位に、ISSCC概要

2016年1月31日より始まる「ISSCC 2016」の概要が明らかとなった。IoE/IoT社会の実現に向けて、デバイス技術やシステム集積化技術の進化は欠かすことができない。特に、電力効率のさらなる改善と高度なセキュリティ技術は一層重要となる。これら最先端の研究成果が発表される。 5Gの携帯電話技術とミリ波通信用周波数生成技術

5Gの携帯電話技術とミリ波通信用周波数生成技術

今回から、2016年1月から2月にかけて米国で開催される半導体関連の国際学会「ISSCC(IEEE International Solid-State Circuits Conference)」を紹介していく。基調講演は、ムーアの法則や5G携帯電話、自動車通信などがテーマになっている。

Copyright © ITmedia, Inc. All Rights Reserved.