【ISSCC 2008】 水晶置き換え狙うCMOS発振器、米Mobius社が偏差90ppm達成:電子部品 タイミングデバイス

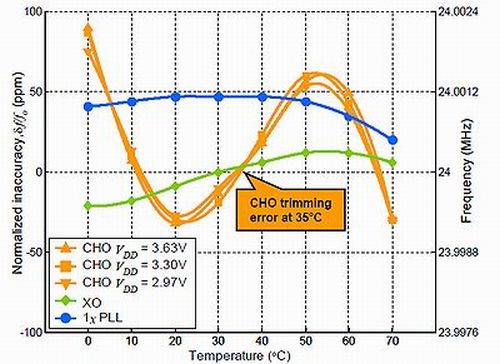

米Mobius Microsystems社は米University of Utahと共同で、CMOS技術で1チップに集積しながらも出力クロック信号の周波数偏差が低いLC発振器を開発し、米国カリフォルニア州サンフランシスコで2008年2月3〜7日に開催された半導体関連の国際学会「ISSCC 2008」で発表した(講演番号は19.6)。24MHzのクロック信号を出力した場合の周波数偏差は、0〜70℃の温度範囲で電源電圧が10%変動した場合でも−30〜+90ppmに収まった。

「電子回路の動作タイミングの基準となるクロック源は、これまでCMOS技術でチップに集積できずに取り残された要素の1つだった」(同社のシニアICデザイン・エンジニアであるScott Pernia氏)。今回の成果で、この状況が変わるという。民生用電子機器に搭載する水晶発振器の置き換えを狙って、今後1〜2年以内にまずは単体のクロック源ICとして製品化する考えだ。将来的には、システムLSIなどに機能ブロックとして集積することを目指す。

周波数偏差を最大90ppmに抑えたことから、参照クロック信号の周波数偏差に対する要求仕様が100〜500ppmのデジタル・インターフェースに使えるという。具体的には、IEEE 1394やPCI Express、シリアルATA3.0、USB 2.0などである。「出力クロック信号の位相雑音密度や周期ジッター(PJ:Periodic Jitter)で比較しても、こうしたデジタル・インターフェース向けの水晶発振器と肩を並べ得る特性を実現できた」(同氏)。使い勝手も高い。すなわち外付け部品は不要で、プリント基板に搭載して電源を供給すれば、開発したチップ単体でクロック信号源として機能する。

MEMS発振器とはすみ分ける

水晶発振器の置き換えやシステムLSIへの集積を狙った発振器としてはすでに、MEMS技術を使ってSi(シリコン)チップに共振器を作り込む手法が実用化されており、例えば米SiTime社が製品を市場に供給している(SiTime社の製品に関する参考記事)。ただしこうしたMEMS発振器には、MEMSプロセスを導入する必要がありCMOS発振器に比べて製造コストが高くなることや、MEMS共振器の占有面積によってチップ寸法が比較的大きくなること、機械的な可動部を備えているため信頼性が比較的低くなるなどの課題があると同社は指摘した。

一方で、「MEMS発振器は、出力クロック信号のキャリア周波数近傍での位相雑音密度が低く、従って周期ジッターが小さいという特徴を備えている。このため、主に無線通信分野の市場で真価を発揮するだろう」(同氏)とし、CMOS発振器とMEMS発振器は応用分野ですみ分けられるとの見解を示した。

トリミングと補償で低偏差を実現

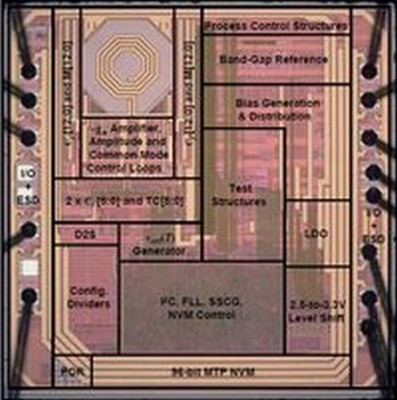

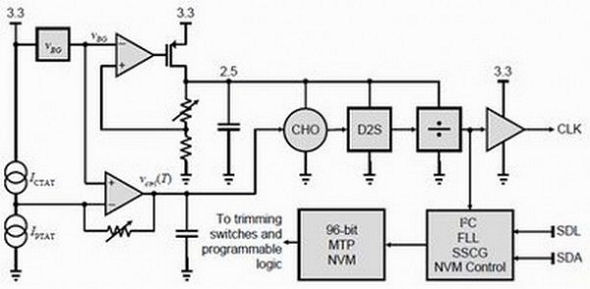

今回開発したのは、「CMOS Harmonic Oscillator(CHO)」と呼ぶ自励発振型のLC発振器である。0.25μmのCMOS技術で製造した。チップ面積は2.25mm2。自励発振周波数は960MHzである。この自励発振周波数を分周してから、最終的なクロック信号として出力する仕組みだ。分周比は2〜2000に設定できる。すなわち480k〜480MHzのクロック信号を出力可能だ。

出力クロック信号を24MHzに設定したときの特性は、位相雑音密度については水晶発振器に比べると若干大きいものの、その差はオフセット周波数が100kHzを下回る領域でも最大11dB/Hz、100kHz以上の領域では最大6dB/Hzに抑えられた。一方で周期ジッターは6.5ps(rms値)と、水晶発振器の8.8ps(rms値)よりも低かった。「ただしこの違いは、出力バッファの駆動能力などに起因したものだ」(同氏)。消費電力は49.5mWである(電源電圧が3.3Vのとき)。

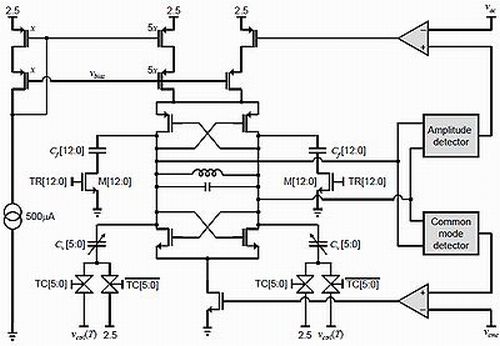

周波数偏差を低く抑えられたのは、トリミング技術と補償技術を活用したからだ。トリミング技術では、LC発振器の発振周波数を決定するコンデンサ(C)の静電容量を調整することで、自励発振周波数を±6%の範囲にわたって、15ppmの分解能で調整できるようにした。静電容量の大きさを2進数で重み付けしたコンデンサを13個並べたアレイを用意し、各コンデンサの接続をトランジスタ・スイッチでオン/オフすることで、アレイ全体の静電容量を細かく調整する仕組みだ。

補償技術では、温度やバイアスの変動と経年変化に起因した周波数ドリフトを抑えた。温度起因のドリフトについては、温度に合わせて出力電圧が変化する電圧源にバラクタ(可変容量ダイオード)を接続することで補償した。バイアス変動や経年変化に起因するドリフトは、LC発振器を構成する能動/受動素子に印加される電圧の振幅を常時監視し、印加電圧が一定値を超えないようにバイアス電流に変調をかける制御ループを使うことなどで補償している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- わずか3個のLSIでモバイル超音波診断装置を実現、ソシオネクスト

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

開発したCMOS発振器のチップ写真。0.25μmのCMOS技術で製造した。チップ面積は2.25mm2である。*1)

開発したCMOS発振器のチップ写真。0.25μmのCMOS技術で製造した。チップ面積は2.25mm2である。*1) 開発したCMOS発振器(図中のCHO)の24MHz出力時の周波数偏差である。水晶発振器(XO)と、水晶発振器にPLL回路を組み合わせたクロック源IC(1xPLL)それぞれの特性と比較した。*1)

開発したCMOS発振器(図中のCHO)の24MHz出力時の周波数偏差である。水晶発振器(XO)と、水晶発振器にPLL回路を組み合わせたクロック源IC(1xPLL)それぞれの特性と比較した。*1) チップ全体の回路のブロック図である。LC発振器コア(図中のCHO)の差動出力をシングル・エンド信号に変換(図中のD2S)し、分周(図中の÷)してからバッファを介して出力する。*1)

チップ全体の回路のブロック図である。LC発振器コア(図中のCHO)の差動出力をシングル・エンド信号に変換(図中のD2S)し、分周(図中の÷)してからバッファを介して出力する。*1) 13ビットの可変容量(図中のCf[12:0])や、6ビットのバラクタ(図中のCv[5:0])を使って、周波数をトリミングしたり温度ドリフトを補償している。*1)

13ビットの可変容量(図中のCf[12:0])や、6ビットのバラクタ(図中のCv[5:0])を使って、周波数をトリミングしたり温度ドリフトを補償している。*1)