不揮発メモリ新時代(後編):メモリ/ストレージ技術(4/5 ページ)

SRAMとフラッシュの置き換えから

現在出荷中のMRAMチップは磁界書き込み方式を採用している*2)。最初にMRAMを製品化した米Freescale Semiconductorは、2008年6月にMRAM部門を米Everspin Technologiesに分社化した。分社後、Everspinは2008年11月に、180nmの製造技術を用いた4Mビット品と1Mビット品の新製品を発表した。44端子のTSOPIIまたは48端子のBGAに封止しており、電源電圧はいずれも3.3Vである。用途はSRAMの代替である。そのため、SRAMインタフェースを備え、書き込み時間は35ns以下である。

*2) スピン注入磁化反転方式については、例えば2007年2月に開催されたISSCC 2007において、日立製作所と東北大学が2MビットのMRAMチップの試作を発表した。

2009年以降は製造技術を130nmに微細化し、書き込み時間を30nsに短縮する予定だ。容量も16Mビットに向上させる。2009年時点での用途はEEPROMやFeRAM、SRAMなどのメモリの置き換えと統合であるとした。

2011年以降はスピン注入磁化反転方式を採用する。65nmの製造技術を適用する予定だ。書き込み時間は10nsを目標にする。インタフェースをDRAMに変更し、容量を64M〜256Mビットまで拡大する予定だ。1Gビット品の投入予定は2015年である。この品種は現在のDRAMと同じDDR3互換にするとした。

ルネサス テクノロジは、米Grandisと共同でスピン注入磁化反転方式を用いた65nmの製造技術を共同開発する契約を結んでおり、将来の製品では同方式を採用するものの、製品化時期は明らかにしていない。

同社はフラッシュマイコンを大量に製造しており、2008年3月には累計出荷個数が13億個に達したと発表した。同社のフラッシュマイコンに使っているフラッシュメモリはMONOS型(Metal Oxide Nitride Oxide Silicon)とNOR型の2つだ。ここに2010年以降、MRAM内蔵型を追加する。2010年には90nmの製造技術を適用した動作周波数100M〜150MHzのマイコンに搭載し、2012年には65nmの製造技術で200MHz動作品に搭載する予定である。いずれもMONOS型、NOR型よりも動作周波数が高いフラッシュマイコンであり、高速化のためにMRAMを用いる。

NECはシステムLSI全体の不揮発化にMRAM技術を用いる。磁界書き込み方式を用いるものの、他社とは異なり、ビット線、ワード線の2本の組み合わせを用いずに磁界を発生させる。磁界を与えるための信号線を1本にとどめた。同社ではこの方式を「一軸書き込み」と呼ぶ。書き込み線をセルごとに用いて高速化した。

NECの方式は1ビットの情報を記録する自由層全体をいきなり反転させるのではなく、2つの磁区の境目である磁壁を移動させることで、反転を進める*3)。「トランジスタが2個必要なために、素子の大きさは1.5倍になるが、磁壁移動の方が、書き込み電流のマージンが広く取れるため、周辺回路が小さくでき、トータルな寸法では問題にならない」(NEC デバイスプラットフォーム研究所で研究部長を務める杉林直彦氏)。さらに書き込み時間は0.5nsに低減できるという。

*3) ISSCC 2008において、杉林氏のグループは同方式を用い、容量32Mバイト、アクセス時間12nsのMRAMチップを発表した。製造技術は90nmである。搭載した非同期SRAM実現回路と合わせたダイの利用効率は63%である。

スピン注入磁化反転方式は、アクセスが高速で大容量のメモリを製造するには適する。ただし、「書き込み時と読み出し時に同じ経路を電流が流れるため、電流値を下げると、誤書き込みが生じたり、書き換え時に過負荷がかかったりする可能性がある。そのため電流値を制御する各種の周辺回路が必要になる。大容量メモリであればメモリ容量に対する周辺回路の比率が下がるため問題にはならないが、小容量で済むシステムLSI用途には負担が重く向かない」(同氏)とした。

このほか新しい用途として、DRAMとNAND型フラッシュメモリを組み合わせた既存のSSDに対して、MRAMとNAND型フラッシュメモリの組み合わせがあり得るとした。

一方、NAND型フラッシュメモリに正面から大容量化で挑むのは難しいという。製造技術の線幅をF(45nmプロセスなら45nm)とすると「MRAMのセルサイズは理想的な場合でも6F2であり、NAND型フラッシュメモリの4F2と比べて1.5倍大きい。さらにNAND型では多値化が使えるため、3ビット(8値)の多値化の場合、製造プロセス換算で2世代半、つまり5年の差が付く。たとえNAND型フラッシュメモリの微細化が止まったとしても、MRAMがNAND型フラッシュメモリと同等の集積度になるにはその後5年間かかると考えている」(杉林氏)。

NAND型並みの集積化が可能なReRAM

ReRAMはPRAMやMRAMよりもさらに基礎的な技術開発の段階にとどまっている。「そもそもどのような物理現象によって書き換えが起こるのかもはっきりしなかった」(エルピーダメモリの安達氏)。製品化はもちろん、素子を並べた小容量品の試作も始まっていない。

それにもかかわらずReRAMの研究開発が進んでいるのは、消費電力、具体的には電流値が下げられること、高速に書き込めること、集積化に向くことが実証されつつあるからだ。産業技術総合研究所によれば、250μAで動作し、書き込み時間は50nsだったという†2)。「これ以上短い時間を測定できる装置がないため、不確実だが、書き込み時の状態変化は実際にはnsオーダーだろう」(産業技術総合研究所でナノ電子デバイス研究センター副センター長とナノテクノロジー研究部門先進ナノ構造グループ研究グループ長を務める秋永広幸氏)。富士通研究所が、2006年に発表した値によると、スイッチング時間は3nsである。

†2) 畑陽一郎、「RRAMで低電流と高速動作を両立、不揮発性メモリの新材料を開発」、EE Times Japan、2008年12月号、no.42、p.28

「素子が小さくできるかどうかということと消費電力の関係は表裏一体ともいえる。特に電流値を下げられるのなら、メモリを構成するダイオードやトランジスタなどの周辺回路を同時に小さくでき、チップが小さく作れる。このため、NAND型フラッシュメモリと同等の集積度も狙える」(秋永氏)。NAND型フラッシュメモリと同等の集積度ならば、現在の半導体プロセスと材料で製造でき、設備投資が少なくて済むこともReRAMの強みであるとした。このため、「DRAM代替候補の第1はPRAM、第2はReRAMだ」(安達氏)、「大容量、高速アクセス、低消費電力という要求が満たせる」(シャープ)というように、ReRAMに対する期待が強い。

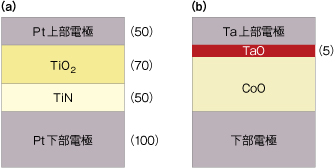

ReRAMは、上部電極と下部電極の間に金属酸化物が挟み込まれた構造を採る(図5)。電圧を印加すると抵抗値が変化し、その後電圧の印加を止めても高抵抗状態と低抵抗状態の2つの安定状態のどちらかを維持する。抵抗値の変化によってメモリ素子として機能するという点ではPRAMと似ている。

動作モードは、正の電圧だけを印加するユニポーラ型と、正負の電圧を印加するバイポーラ型がある。素子当たり1つのトランジスタだけで動くユニポーラ型が集積度の点では有利だが、「2008年末の時点ではトランジスタが2つ必要なバイポーラ型の方が性能が高く、当初のチップはバイポーラ型になるだろう」(秋永氏)。産業技術総合研究所が開発した構造を採った場合の動作モードは以下の通り。ある一定値よりも高い正電圧を印加すれば、高抵抗状態から低抵抗状態に変化する。負電圧を印加することで逆方向の変化が起こる。正電圧として2.2V、負電圧として−1.4Vで動作した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

図5 ReRAM素子の構造 電極間に金属酸化物がはさみ込まれた構造を採る。(a)富士通研究所の構造、(b)産業技術総合研究所の構造。TaOは自発的に形成される。かっこ内は厚さで、単位はnm。

図5 ReRAM素子の構造 電極間に金属酸化物がはさみ込まれた構造を採る。(a)富士通研究所の構造、(b)産業技術総合研究所の構造。TaOは自発的に形成される。かっこ内は厚さで、単位はnm。