強誘電体SRAMやスピンMOS FETが開発、新材料や新機構で微細化限界打ち破る(後編):デバイス技術

東芝が開発したスピンMOS FETは、2015年以降の実用化を目指した将来技術である。ピンMOS FETとは、前述のように、電子のスピン情報(スピン方向の違い)を使って動作を制御する新規デバイスだ。

スピンMOS FETの動作を実証

一方の東芝が開発したスピンMOS FETは、2015年以降の実用化を目指した将来技術として位置付ける。前述の東大の竹内氏の研究グループのさらに先を見据えた取り組みだと言える(図1)。

スピンMOS FETとは、前述のように、電子のスピン情報(スピン方向の違い)を使って動作を制御する新規デバイスである。ゲート電圧を変えることで、ソース・ドレイン電流を制御できる点は一般的なMOS FETと何ら変わらない。

ただ、アップ・スピンの電子だけが電気伝導に寄与するなど、従来とは動作機構が大きく異なる。電子のスピン方向の差異による抵抗差が、MOS FETのオン/オフに対応することになる。従来と動作機構が異なるため、待機時や動作時の消費電力の増大といった微細化に起因したさまざまな課題を解決できるとする。具体的には、「消費電力が低く、高速動作が可能という特長がある」(東芝研究開発センターの斉藤氏)。

微細化しやすいMOS構造を採用

東芝の開発内容の新規性はまず、微細化しやすく、Si材料のCMOSと親和性が高いMOS構造を採用したこと。さらにその上で、このスピンMOS FETの動作を実際に確認したことにある。

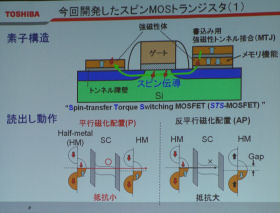

試作したスピンMOS FETの構造は、ソース電極とドレイン電極それぞれに磁性層を設けたもの。ソース/ドレイン部分のSi上にトンネル障壁層を介して、ハーフ・メタルの一種であるホイスラ合金(Co2FeAl1-xSix)を積層した。磁性層が、電子のスピン情報を保持する役割を担い、ソース電極とドレイン電極のスピンが一致している場合(平行状態)は抵抗が小さく、一致していない場合(反平行状態)では抵抗が大きくなる仕組みである(図2)。

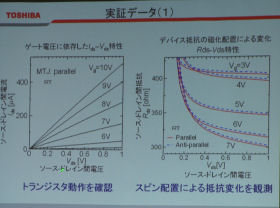

図左(図2)は、スピンMOS FETの構造。上部は開発したスピンMOS FETの構造、下部はバンドギャップ構造を示している。ソースとドレインのスピンが平行になることで、抵抗が下がる。一方、反平行時には抵抗が大きくなる。抵抗の大小が、オン/オフに対応する。電子のスピン方向は、「スピン注入磁化反転技術」を使って変える。図右(図3)は、基本動作試験の結果。左図はソース・ドレイン電圧に対するドレイン電流の変化の様子。右図は、スピン方向の差異による、抵抗値変化の様子を示している。赤線がスピン方向が平行配置の場合、青線は反平行配置の場合である。抵抗差は、数Ω程度。

図左(図2)は、スピンMOS FETの構造。上部は開発したスピンMOS FETの構造、下部はバンドギャップ構造を示している。ソースとドレインのスピンが平行になることで、抵抗が下がる。一方、反平行時には抵抗が大きくなる。抵抗の大小が、オン/オフに対応する。電子のスピン方向は、「スピン注入磁化反転技術」を使って変える。図右(図3)は、基本動作試験の結果。左図はソース・ドレイン電圧に対するドレイン電流の変化の様子。右図は、スピン方向の差異による、抵抗値変化の様子を示している。赤線がスピン方向が平行配置の場合、青線は反平行配置の場合である。抵抗差は、数Ω程度。データ書き込み(スピン方向の制御)には磁気トンネル接合(MTJ)素子を使い、これをソース電極とドレイン電極のいずれか、または双方に積層する。「スピン注入磁化反転技術」を使って、スピン方向を変える点も特徴である。

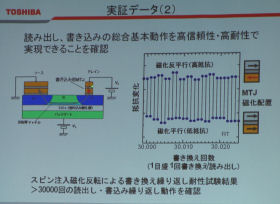

この構造のスピンMOS FETを使って、ゲート電圧に応じてソース・ドレイン電流が変わることや、スピン方向を変えることでソース・ドレイン間の抵抗値が変化すること、低抵抗状態と高抵抗状態を書き換えたりこの情報を読み出せたりすることを確認した(図3)。さらに、情報の書き換えを3万回以上繰り返せる信頼性があることも確認した(図4)。

「このように総合的に基本動作を確認したのは業界初。スピンMOS FETの実用化に向けた研究開発はスタートしたばかりで、基本動作の確認は小さな一歩だけれども、実用化に向けて意義のある大きな一歩だ」(同氏)と意義を説明した。

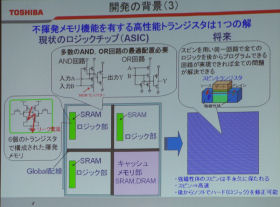

図左(図4)は、書き換え耐性試験の結果。書き込み/読み出し動作を、3万回以上繰り返せることを確認した。図右(図5)は、スピンMOS FETの開発背景。スピンMOS FETを採用したロジック回路が開発できれば、再構成可能で不揮発なシステムLSIを実現できるとする。

図左(図4)は、書き換え耐性試験の結果。書き込み/読み出し動作を、3万回以上繰り返せることを確認した。図右(図5)は、スピンMOS FETの開発背景。スピンMOS FETを採用したロジック回路が開発できれば、再構成可能で不揮発なシステムLSIを実現できるとする。スピン・トランジスタとしてはこれまで、チャネル部分にIII-V族の半導体材料を使った「Datta&Das型」と呼ぶ構造が知られていた。ただ、125nmより長いチャネル長が必要で、微細化に向かない。「この構造での実用化は難しいとされてきた」(同氏)という。

なお、東芝が採用したスピンMOS FETの構造そのものは、2004年に東京工業大学の菅原聡氏と東京大学の田中雅明氏が提唱した構造である。試作例もあったが、これまでは、スピン状態が伝わるという動作を確認するにとどまっていたという。

トンネル障壁部の成膜技術が鍵

今後の課題は、界面抵抗を小さくすることや、抵抗差を大きくすることである。

磁性体とSiの間の界面抵抗は、最も下げられる条件のとき20Ω程度で、スピン方向が変わったときの抵抗差は数Ωである。界面抵抗を下げ、抵抗差を大きくするには、トンネル障壁部分の成膜技術や、ホイスラ合金の改善が鍵を握るという。今回、トンネル障壁層の材料には、SiOx(酸化シリコン)またはMgO(酸化マグネシウム)を採用した。このトンネル障壁層の材料についても検討を進めているところだという。

東芝の斉藤氏は、スピンMOS FETを採用したロジック回路が実現すれば、「ロジック回路の世界をがらりと変えられる可能性がある」と意気込みを語った(図5)。スピンMOS FETでは、スピン方向が磁性体で保持されるため、不揮発になるという特長もある。ロジック回路を構成するMOS FETにメモリー機能を持たせることが可能で、再構成可能で不揮発なシステムLSIを実現できるという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

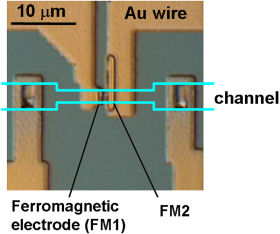

図1 東芝が開発したスピンMOS FET スピンMOS FETを試作し、基本動作を検証した。

図1 東芝が開発したスピンMOS FET スピンMOS FETを試作し、基本動作を検証した。