開発進む不揮発メモリReRAM、新材料からチップ化まで技術がそろう:メモリ/ストレージ技術 ReRAM(2/2 ページ)

22nm世代の製造に適するReRAM

ReRAMは、国際半導体技術ロードマップ(ITRS:International Technology Roadmap for Semiconductors)が規定する22nm世代のテクノロジーノードでの製造に適した不揮発メモリとして期待を集めている。従来のフラッシュメモリではこれ以上縮小が難しいとされてきたビット当たりのセル面積を、さらに縮小できそうだ。現在、富士通やシャープ(関連記事「128KビットのReRAM素子を試作」参照)、米Hewlett Packard(HP)社などの企業がReRAMの設計に取り組んでいる。

この他、米Advanced Micro Devices(AMD)社からスピンオフした新興企業である米Adesto Technologies社は、米Axon Technologies社からReRAMに適用するPMC(Programmable metallization Cell:プログラマブルメタライゼーション・セル)技術のライセンス提供を受けたという。PMCは、米Arizona State Universityが開発した、エネルギ効率に優れた大容量メモリを低コストで実現できるメモリ技術である。

さらに、欧州では、ベルギーの研究機関であるIMEC(Interuniversity Microelectronics Center)が、韓国Samsung Electronics社や韓国Hynix Semiconductor社、エルピーダメモリ、米Micron Technology社などのパートナー企業と提携して、独自にReRAMの研究開発を進めている。

Missouri S&Tの研究チームが発表した超格子材料には、2種類の異なる組成のFeO・Fe2O3を積層したものと、2種類の異なる組成のZnxFe3-xO4を積層したものとがある。試作した超格子材料は、印加された電圧に応じてさまざまな抵抗値を示す。Missouri S&TのSwitzer氏は、超格子材料の抵抗値を3段階以上に設定できることも発見している。こうした特性を備えていれば、1つのセルに複数ビットの情報を記録する多値化技術への道が開ける。

Missouri S&Tの研究チームはめっき技術を使って超格子を成長させた。具体的には、溶液中で2枚の単結晶Au(金)電極の間に電位差を作り、超格子を形成した。Switzer氏は、「われわれの技術は、超格子を電気めっきで作る点が画期的だ。形成する超格子の層ごとにAu電極に印加する電圧を変えることで実現した」と説明する。同氏の研究チームは今後、他の材料を試し、超格子の持つ潜在的なメカニズムの解明を目指したいとしている。超格子材料が記憶を保持できる時間がどのくらい長いのかも明らかにするという。

シャープとアルバックが128KビットのReRAM素子を試作

シャープとアルバックは2010年2月、8インチウエハ上に形成した128KビットのReRAMチップを公開した(図A-1、図A-2)。ReRAMとしては世界初のチップ化という。メモリセルは1トランジスタ1抵抗(1T1R)構成。

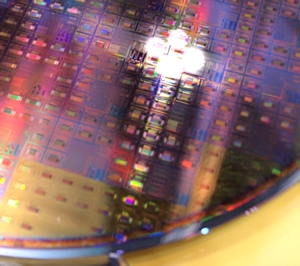

図A-1 8インチウエハ上に形成したReRAMチップ シャープが開発した。標準CMOS技術だけを用いて約100個のダイを形成した。1つのダイ上に2Kビット〜128Kビットと容量の異なる特性評価素子(TEG)を約16個含む。

図A-1 8インチウエハ上に形成したReRAMチップ シャープが開発した。標準CMOS技術だけを用いて約100個のダイを形成した。1つのダイ上に2Kビット〜128Kビットと容量の異なる特性評価素子(TEG)を約16個含む。両社は、新エネルギー・産業技術総合開発機構(NEDO)の支援を受け、産業技術総合研究所や大阪大学とReRAMに関する共同研究を進めてきた。例えば、産業技術総合研究所は2008年9月、250μAという低電流で動作し、50nsで内容を書き換えられるReRAM向けの材料を開発したと発表している。下部電極(材料は非公開)とTa(タンタル)上部電極の間にCoO(酸化コバルト)を挟み込むと、CoOとTa上部電極の間に厚さ5nmのTaO(酸化タンタル)層が自然に形成されることが特長だ。さらに高抵抗状態から低抵抗状態へ切り替えるときにTaO層に形成される電流路(カレントパス)が直径数nmと小さいことが特長だ。従来のPt(白金)電極ではこのような現象を起こせないため、CoO中を流れる電流量を十分引き下げることができなかった。

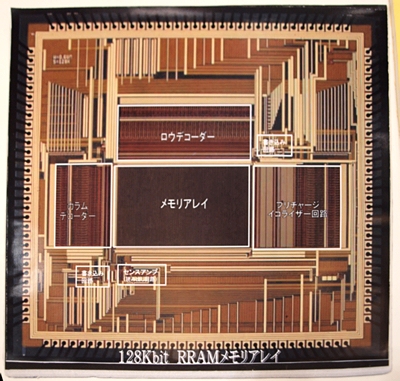

図A-2 ReRAMチップのダイの拡大写真 チップ寸法は約5mm角。128KビットのReRAMのメモリアレイの上と左にデコーダ回路が、右上と左下には書き込み回路が、左下には読み出し用のセンスアンプがレイアウトされている。チップ上にレイアウトした読み出し、書き込み回路を用いて、メモリセルの読み出し、書き込み動作を検証したという。

図A-2 ReRAMチップのダイの拡大写真 チップ寸法は約5mm角。128KビットのReRAMのメモリアレイの上と左にデコーダ回路が、右上と左下には書き込み回路が、左下には読み出し用のセンスアンプがレイアウトされている。チップ上にレイアウトした読み出し、書き込み回路を用いて、メモリセルの読み出し、書き込み動作を検証したという。今回のシャープのチップはこのとき開発した材料を用いている。シャープの研究開発本部基盤技術研究所第五研究室で主任研究員を務める大西茂夫氏は、「書き込み電流は250μAを下回る。今回の成果を2010年5月に学会発表した後、2010年9月までに信頼性評価を終える」とした。

関連記事

不揮発メモリ新時代(前編)

不揮発メモリ新時代(前編)

今後、メモリは全て不揮発になる。機器の機能向上につれて、増えたシステム全体の消費電力を抑えるのに、メモリの不揮発化が役立つからだ。メモリが不揮発化すれば、ほかのメリットも生じる。例えばデジタル家電を瞬時に起動できるようになる。PCの起動やシャットダウン操作が不要になる。 不揮発メモリ新時代(後編)

不揮発メモリ新時代(後編)

現在のDRAMやNAND型フラッシュメモリの用途に向けた次世代不揮発メモリの候補は4種類ある。FeRAM、MRAM、PRAM、ReRAMだ。ただし、どれか1つの不揮発メモリで全用途に対応することは難しそうだ。これはどの不揮発メモリにも何らかの欠点が存在するからだ。後編では不揮発メモリの用途や各不揮発メモリの性能向上策、技術動向について解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速