第19回 差動対がオペアンプに変身(4)〜オープン特性を1次傾斜へ〜:Analog ABC(アナログ技術基礎講座)(2/2 ページ)

位相余裕と利得余裕を確保

オペアンプを設計する上で、この位相余裕と利得余裕は大切な指標です。詳しく説明しましょう。

負帰還をかけたオペアンプが発振してしまう条件は、主に2つあります。1つは、入力信号よりも大きくなって信号が戻ってくること。もう1つは、入力信号と同じ位相で戻ってくることです。すなわち、入力信号より大きくて同位相の信号が、どんどん入力信号に足し合わされることになるので、発振してしまいます。

このとき、利得余裕と位相余裕とは、発振してしまう状況から、利得と位相がどれだけかけ離れているかを示しています。具体的には、位相余裕とは利得が0dBにまで下がったときの、入力信号に対する出力信号の位相です。この値が0度から離れているほど、余裕があることになります。

入力信号と出力信号が同相とは位相が0度のことですので、位相余裕とは同相になるどれぐらい手前で、位相の変化が止まっているかを表しています。一方の利得余裕とは、位相が0度になったとき、利得がどれだけマイナスになっているかを示します。利得がマイナスになると、増幅回路が入力信号を増幅しているのではなく、減衰していることになります。すなわち、入力信号よりも出力信号は小さくなり、発振しなくなります。

LとCの活用でシミュレーション

位相余裕と利得余裕を確認するには、利得の高い増幅回路をオープン状態で交流解析する必要があります。このとき、動作点の設定には十分な注意が必要です。オペアンプの2つの入力端子である正転/反転入力端子の入力電圧を1μV単位で調整しないと、増幅回路の利得が高いために、電源電圧やグラウンド電圧に出力電圧が張り付いてしまって(達してしまって)、正しくシミュレーションを実行できないことがあります。

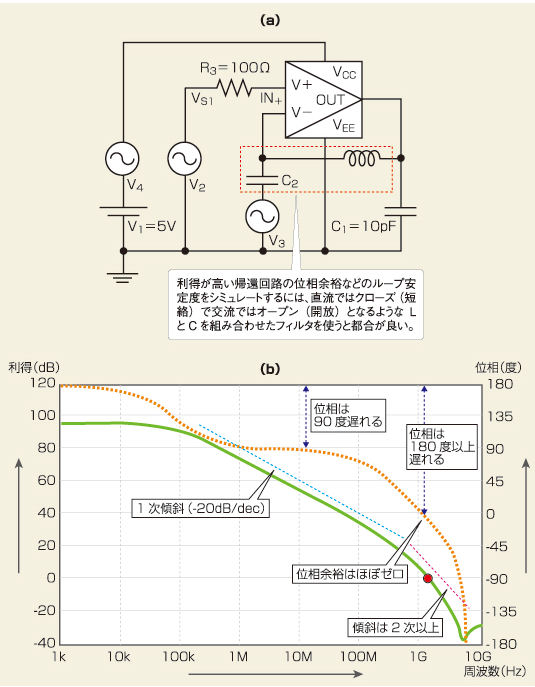

そんなときには、図4(a)のように、帰還をかけながら交流解析する方法があります。直流成分はインダクタを介して帰還がかかっているので、出力が電源電圧やグランド電圧に張り付くことはありません。解析結果を知りたい周波数では、インダクタのインピーダンスを十分に大きくし、逆にコンデンサのインピーダンスは小さくすることで、オープン状態での交流解析を実施できます。

図4 オペアンプが安定して動作するか利得余裕と位相余裕を確認 オペアンプのように利得の高い増幅回路をオープン状態で交流解析をするときは、動作点の設定に十分な注意が必要です。このときは、(a)のようにLとCを組み合わせて帰還をかけながら解析すると便利です。(b)は、解析した結果の周波数特性です。実線は利得特性、破線は位相特性です。位相特性を見ると、利得が0dBの周波数での位相遅れ(位相余裕)が、ほぼゼロであることが分かります。

図4 オペアンプが安定して動作するか利得余裕と位相余裕を確認 オペアンプのように利得の高い増幅回路をオープン状態で交流解析をするときは、動作点の設定に十分な注意が必要です。このときは、(a)のようにLとCを組み合わせて帰還をかけながら解析すると便利です。(b)は、解析した結果の周波数特性です。実線は利得特性、破線は位相特性です。位相特性を見ると、利得が0dBの周波数での位相遅れ(位相余裕)が、ほぼゼロであることが分かります。上記の方法に従って、図4(a)をシミュレーションを実行して周波数特性を求めると、図4(b)が得られました。ここでは位相余裕を確認してみましょう。

まず、図中の実線で示した利得特性を見ると、100kHzまでは利得は100dBより少し低い値で変化なく推移していますが、100kHzを境に大幅に低下していきます。100kHzから600MHz付近の範囲は利得の変化は1次傾斜となり、600MHz以上の周波数になると、2次以上の傾斜になります。

次に、位相特性を見ましょう。周波数が1kHzのときの位相は180度です。負帰還をかけていますので、入力信号と出力信号は逆相、つまり位相が180度の状態が基準となります。周波数が10kHzを越えた付近から徐々に位相は180度から小さくなっていきます。すなわち、位相がゆっくりと遅れていきます。1MHzを越えた付近から位相の変化がなくなり、再度60MHzを越えた付近から位相が遅れていきます。

利得特性の傾斜と位相には、密接な関係があることに気づいたでしょうか。詳細な説明は別の機会にしたいと思いますが、利得特性の傾斜が1次(-20dB/dec*1))の区間では、位相は90度遅れとなります。傾斜が2次になると位相は180度遅れ、傾斜が3次となると位相は270度遅れることになります。

利得が0dBのときの位相余裕を確認してみると、ほぼゼロです。ほとんど位相余裕が無く、いつ発振してもおかしくない状態です。位相余裕を確保するためには、利用したい周波数範囲で利得特性を1次傾斜のまま、0dBを通過させることが重要になります。そうすれば、位相余裕は理想的には90度になります。

実際の位相余裕の目安は、回路設計者それぞれの感覚に依存します。40度〜60度が目安でしょうか。位相余裕が60度あれば、発振するおそれは少ないといえます。ところが、40度を切ると、周囲温度や電源電圧の変化、製造技術の差異が原因で発振してしまう恐れが高くなると思います。

位相変化のセオリー

図3(b)の説明からも分かるように、利得特性が1次傾斜から2次傾斜に変わった周波数で、位相が90度から180度に急激に変化する訳ではありません。位相は利得特性の傾きに応じて、ゆっくりと遅れていきます。

この位相特性の変化にはあるセオリーがあります。例えば、利得特性が0次傾斜から1次傾斜に変わった周波数(100kHz)の1桁ほど小さい周波数(10kHz)で、位相は180度からゆっくりと遅れ始めます。そして、0次傾斜から1次傾斜に変わった周波数の1桁高い周波数(1MHz)で位相の変化が止まり、位相が90度の状態になります。

利得特性の傾斜が変わった(周波数)より1桁小さい周波数から位相は遅れはじめ、1桁大きい周波数付近で位相の変化が止まる、これが周波数特性のセオリーといえます。

このことを知っておくと、設計した回路をシミュレーションを実行しなくとも周波数特性の全体像を知ることができます。利得特性は、回路の設計に使った部品の定数を基に計算式で求められます。利得特性が分かってしまえば、上のセオリーに基づいて、位相特性を描くことができるのです。

位相余裕のない状態を改善するためには、コンデンサを増幅回路に追加し、応答速度を遅くして、位相余裕を増やすのが一般的です。次回は、コンデンサを追加して得られる効果を説明しましょう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- わずか3個のLSIでモバイル超音波診断装置を実現、ソシオネクスト

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」