目指すは待機電力ゼロの夢のLSI、東北大が磁性素子利用の不揮発ロジックを実証:プロセス技術 不揮発ロジック(1/2 ページ)

もはや、従来技術の延長ではこれ以上の消費電力の削減は見込めない。今まさに、半導体チップの基本デバイスの根本的な変革が必要な時期を迎えている。

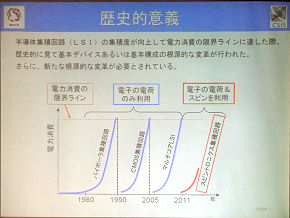

バイポーラトランジスタ集積回路から、CMOS集積回路、マルチコア回路へ――半導体技術の進歩を思い返すと、消費電力の観点で限界に達すると、新しい革新的な技術が実用化されてきた。従来技術の延長ではこれ以上の消費電力の削減は見込めない段階にきており、今まさに半導体チップの基本デバイスの根本的な変革が必要な時期を迎えている。東北大学スピントロニクス集積化システムセンターのセンター長を務める大野英男氏は、このように語る。

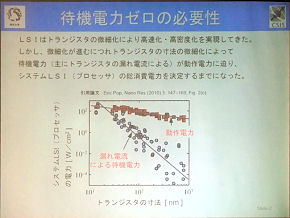

これまでは、半導体チップの製造プロセスの微細化が、消費電力の問題を解決する手段とされていた。一般に、処理性能と消費電力は、トレードオフの関係にあり、処理性能を上げようとすると、消費電力量も上昇してしまう。しかし、微細化を進めると、消費電力を引き下げつつ、処理性能を高められる。微細化の恩恵によって、半導体チップは、高速化と高密度化を進めてきた。

ただ、このような手法も、限界を迎えている。微細化が進展するにつれて、トランジスタの待機電力(主に、漏れ電流が寄与)が、無視できなくなってきたからだ。システムLSIは膨大な数のトランジスタで構成しており、それぞれのトランジスタの漏れ電流がわずかだとしても、全体としては無視できない。最先端の製造プロセスでは、何も動かしていないときの電力(待機電力)の総量が、動作時の消費電力に匹敵するに至っているのだ。

半導体集積回路の集積度が向上して、消費電力の限界ラインに達したとき基本デバイスが変化してきた(図左)。微細化が進展したことで、待機時の消費電力の総量が動作時の消費電力に匹敵するまでに増大している(図右)。

半導体集積回路の集積度が向上して、消費電力の限界ラインに達したとき基本デバイスが変化してきた(図左)。微細化が進展したことで、待機時の消費電力の総量が動作時の消費電力に匹敵するまでに増大している(図右)。「スピントロニクス」が次世代の基本デバイス

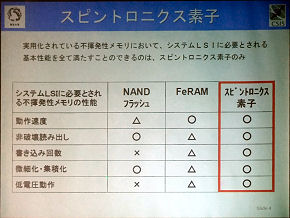

基本デバイスの根本的な変革とは何か。前出の大野氏は、電子の電荷のみならず、スピンも回路の動作に使う「スピントロニクス集積回路」が、次世代の基本デバイスになると主張する。同氏の研究グループは実際に、スピントロニクス集積回路の適用例として、スピン注入磁化反転型磁気トンネル接続(MTJ)素子を使った不揮発ロジックを実証した。

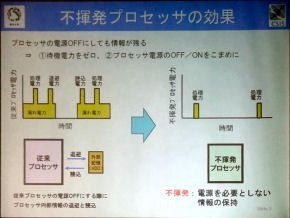

電荷のみならずスピンの状態も利用するメリットは、回路の状態を保持できる点にある。電子のスピンは、外部から磁界を掛けるなどして変化させなければ、その方向を維持する。従って、スピンの方向で情報を記録するメモリを実現すれば、電源を遮断した状態でも、データを保持できる。電源を遮断することで、待機電力をゼロにできるというわけだ。

もちろんこれまでも、スピントロニクスをキーワードにした研究開発は、活発に進められてきた。今回の大野氏の研究グループの成果の意義は、「システムLSIとして呼べる形で、スピントロニクスを使った不揮発ロジックの動作を実証した」(大野氏)という点にある。不揮発ロジックを使ったシステムLSIの実用化には、まだまだ多くの課題があるが、「実用化を目指す上で乗り越えるべき、スレッショルド(しきい値)」を超えたことに相当する成果である」(同氏)という。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

写真左は、東北大学スピントロニクス集積化システムセンターのセンター長を務める大野英男氏。写真右は、東北大学電気通信研究所の教授である羽生貴弘氏。共同で研究を進めた。

写真左は、東北大学スピントロニクス集積化システムセンターのセンター長を務める大野英男氏。写真右は、東北大学電気通信研究所の教授である羽生貴弘氏。共同で研究を進めた。