ルネサス、コストかけずに高速I/O搭載LSIを実現する設計技術開発:プロセス技術(2/2 ページ)

多段の分布定数インピーダンスマッチング技術

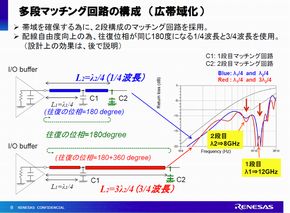

より反射波が多く発生する10Gビット/秒を上回る高速信号転送時でも、信号劣化を抑える技術としてルネサスは今回、多段の分布定数インピーダンスマッチング技術を開発した。

12.5Gビット/秒のOIF規格をクリア

今回開発した多段マッチング技術では、スルーホールに加えて、ビルドアップ型パッケージ基板に存在する「ビア」の寄生容量でも逆位相波を発生させる2段構成とした。1段は、従来と同じ1/4波長の反射波を発生させ、もう1段は3/4波長(往復位相が360°+180°で逆位相になる)を発生させ、より多くの反射波を打ち消すというものだ。

2段のマッチング回路を用いることで、12.5Gビット/秒のOIF規格*)を満たす信号品質を確保できることを確認。ルネサスでは、「今回開発した技術で、理論的に25Gビット/秒まで対応できる見込み」とし、今後の高速インタフェース搭載LSIに広く適用できる技術としている。

*)各種インタフェースの標準規格を制定する団体「OIF」(Optical Internetworking Forum)の定めた規格で、許容信号反射量は−8dB以下と定められている

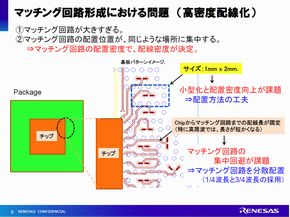

分布定数インピーダンスマッチングの課題も解決

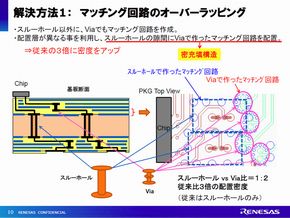

さらに多段化に伴い、分布定数インピーダンスマッチング技術の欠点も解消された。従来の1段でのマッチング技術では、逆位相波を発生させるマッチング回路(スルーホール)を高密度に配置することが難しかった。これは、チップとスルーホールの配線長で位相を調整するため、スルーホールの配置位置が同じような場所に集中し、マッチング回路を形成できる数に限りがあった。特に、高周波であれば、チップとスルーホールの配置位置が近くなるため、多数の高速インタフェースを持つLSIに、この技術を適用するためには、マッチング回路を高密度に配置する技術が必要になっていた。なお、1段目にスルーホール、2段目にビアをマッチング回路を形成した場合と、その逆で回路を形成した場合での効果に、「ほぼ差異はない」という。

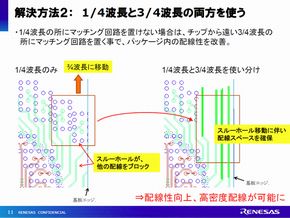

開発した多段マッチング技術では、スルーホール以外にビアを使用するため、スルーホールの上層、下層にマッチング回路であるビアを形成できるため、「従来に比べ3倍の密度で、マッチング回路を形成できるようになった」とする。

3倍の配線密度を達成し、100チャンネルLSIも可能に

加えて、1/4波長よりも、配線長が長くなる3/4波長を使用することにより、マッチング回路の配置場所をよりチップから遠い場所にまで広げることができるため、配線性がより高まり、高密度で広くマッチング回路を配置できるようになり、「100チャンネルの高速I/Oを持つLSIにも適用できるようになった」とする。

開発した技術をデバイスに搭載する場合にも、「チップに特別な回路を作らないだけでなく、パッケージ基板製造時に追加的な加工の必要性もない。既に、ビア、スルーホール、配線などを3次元形状の分布定数部品としてライブラリー化し、容易にパッケージ基板を設計できる開発環境も整備している」とし、現在、開発段階にあるASICなどのLSIに新技術の提供を進めている。

- FD-SOIがついに大規模量産で日の目を見るのか? STの戦略を読み解く

- 次世代組み込みプロセッサ向け18nmプロセス技術、FD-SOIと相変化メモリがベース

- 生合成した共重合体とのブレンドで、ポリ乳酸の靭性と生分解性を改善

- 浮体式ペロブスカイト太陽電池の共同実証実験を東京都北区のプールで開始

- 「M3 MacBook Air」は衝撃的なファンレスモバイル Windowsの世界よりも2歩先を進んでいる

- TSMCの詳細判明、台湾地震による半導体工場の最新被害/稼働状況

- 「3D NANDの進化」に必要な要素とは

- 「必要な性能の半導体が欲しいときに入手できない」、企画力向上急ぐ

- 「30年に3000億円規模」のシリコンキャパシター市場、後発ロームが見いだす勝機とは

- ST、次世代「STM32」マイコンに向けたプロセス技術を発表

関連記事

ルネサスが0.2V対応電源ICを開発し、電波によるエネルギーハーベスティングシステムを実現

ルネサスが0.2V対応電源ICを開発し、電波によるエネルギーハーベスティングシステムを実現

ルネサス エレクトロニクスは、電波エネルギーから電気エネルギーを取り出し、マイコンや温度センサーを駆動させるシステムを開発した。0.2Vという低電圧を昇圧する技術などの技術を盛り込んだ。 ルネサス、8四半期ぶりに営業黒字達成も再建策は「まだ」

ルネサス、8四半期ぶりに営業黒字達成も再建策は「まだ」

ルネサス エレクトロニクスは2013年5月9日、2012年度(2013年3月期)決算を発表した。第4四半期(2013年1〜3月期)は、8四半期ぶりとなる四半期ベースでの営業黒字を達成した。再建に向け光明が少し見え始めるも、2013年度の業績見通しや具体的な再建策については、「まだ策定中」(ルネサス社長)として公表しなかった。 【ESEC2013】ルネサス再建の先駆事例へ、スマートバイオ向けプラットフォームをデモ

【ESEC2013】ルネサス再建の先駆事例へ、スマートバイオ向けプラットフォームをデモ

ルネサス エレクトロニクスは、単純な半導体デバイス販売ビジネスだけでなく、「すぐに半導体製品が使える」ように、ソフトウェア技術やモジュール化技術などを含めたソリューション型ビジネスモデルを強化している。その一環として、「スマートバイオ」に向けたソリューション構築を進め、「第16回 組込みシステム開発技術展(ESEC2013)」(2013年5月8〜10日、東京ビッグサイト)で畜産用途向け生体モニタリングシステムの展示を行った。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速