サムスンとSK Hynix、ISSCCで次世代メモリを披露:メモリ/ストレージ技術

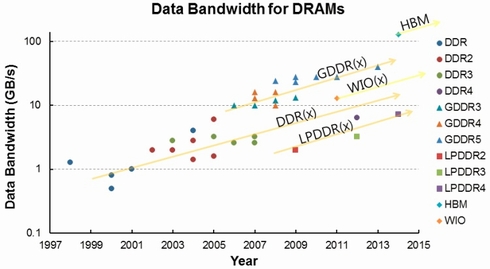

Samsung Electronics(サムスン電子)とSK Hynixは、2014年に開催される半導体集積回路技術の国際会議「ISSCC 2014」で、LPDDR4や広帯域メモリ(HBM)など、次世代のメモリを披露する。

Samsung ElectronicsとSK Hynixは、2014年2月に米国カリフォルニア州サンフランシスコで開催される「ISSCC(IEEE International Solid-State Circuits Conference) 2014」でそれぞれリポートを発表し、ローエンドとハイエンドのメモリチップの未来について説明するようだ。

Samsungは、低消費電力のスマートフォン向けLPDDR4を公開する。電圧1.0V、端子当たりの帯域幅は3.2Gビット/秒だという。同チップは25nmプロセスを用いて製造される。

ISSCCの主催者によると、これらのチップは、これまでに発表された中で最も速い転送速度と最も高い密度を実現しているという。2014年内には、既存のLPDDR3チップの代替メモリとして、スマートフォンなどへの導入が始まるとみられている。

LPDDR4メモリとは別に、Samsungは、0.064mm2のSRAMセルを発表する予定だ。同SRAMセルは、14nm世代のFinFETプロセスで製造されるという。

SK Hynixは広帯域メモリ(HBM: High-Bandwidth Memory)を初公開する。8Gビットのこのメモリは、シリコン貫通電極(TSV)を使って4個のダイを積層したもので、29nmプロセスを用いて製造されている。電圧は1.2V、メモリ帯域幅は128Gバイト/秒を実現する。8チャンネルをサポートし、1024本のI/Oを備える。

ライバルであるMicron Technologyは、HBMに似た「Hybrid Memory Cube(HMC)」と呼ばれるメモリスタックの開発計画を打ち出している。HMCは、通信、グラフィックス、サーバといった分野に向けるという。Micronは既に、HMCのサンプル出荷を開始している。容量は4Gバイト、メモリ帯域幅は160Gバイト/秒だ。

【翻訳:青山麻由子、編集:EE Times Japan】

関連キーワード

Samsung | DDR4 | ISSCC | LPDDR | DRAM | Hybrid Memory Cube | SRAM | メモリ/ストレージ技術(エレクトロニクス) | Micron

関連記事

次世代メモリ「HMC」の仕様バージョン1を公開

次世代メモリ「HMC」の仕様バージョン1を公開

DRAMチップを3次元方向に積層し、シリコン貫通電極で接続するHybrid Memory Cube(HMC)。転送速度が大幅に高速化するHMCが早期に製品化されれば、あらゆる機器に大きな改善をもたらすだろう。 サムスン電子が「業界初」の3次元NANDを量産

サムスン電子が「業界初」の3次元NANDを量産

Samsung Electronics(サムスン電子)は、メモリセルを垂直に積層した3次元セル構造のNAND型フラッシュメモリの量産を発表した。記憶容量は128Gビットで、セルの積層数を増やすなどすれば、将来的には1テラビット容量も可能だという。 サムスン電子、DDR4メモリの量産を開始

サムスン電子、DDR4メモリの量産を開始

Samsung Electronics(サムスン電子)は、4GビットDRAMをベースにしたDDR4メモリモジュールの量産を開始した。20nmのプロセスを適用していて、2.667Gビット/秒の転送速度を実現している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速