A-Dコンバータを用いた新方式PLLを開発:新技術(1/2 ページ)

東京工業大学は2015年3月10日、同大学教授の松澤昭氏らの研究グループが、A-Dコンバータを用いた新しい方式のデジタルクロック生成器の開発に成功したと発表した。

東京工業大学は2015年3月10日、同大学教授の松澤昭氏らの研究グループが、A-Dコンバータを用いた新しい方式のデジタルクロック生成器の開発に成功したと発表した。従来のデジタルPLL(Phase Locked Loop:位相同期ループ)に比べ、低消費電力、低ジッタで動作することを確認したという。

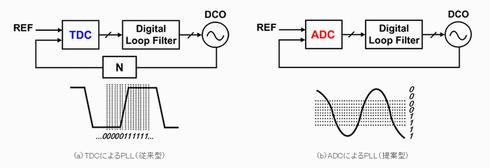

クロック生成回路は、低ジッタかつ低消費電力であることが求められる。クロック生成には、通常、PLLが用いられるが、従来のアナログ方式のPLLでは、フィルタの面積が大きいという問題を抱え、より小型化できるデジタルフィルタを用いるデジタルPLLの開発が進んでいる。

デジタルフィルタは、フィルタ部分の面積を縮小でき、所望の周波数に達するまでのロック時間を短くできる特徴を持つ。なお、デジタルPLLでは、発振器の出力を分周した信号と基準信号との時間差を検出する時間差デジタル変換器(Time to Digital Converter/以下、TDC)が用いられる。

帰還ループのデジタル化は、柔軟、堅牢な制御が行える一方で、TDCの時間分解能をあまり高くできず、それによりジッタが劣化するという欠点がある。具体的には、TDCの時間分解能が粗いと、帯域内位相雑音が劣化し、ジッタが大きくなる。

時間差よりも電圧差で

これに対し、松澤昭氏と同大学准教授 岡田健一氏らの研究グループは、時間差を検出するよりも、電圧差の方が高精度で検出できることに着目し、TDCの代わりにA-Dコンバータを用いるPLLを考案した。

デジタルPLLの校正。デジタル型位相同期回路(PLL)において、従来は時間デジタル変換器(TDC)が用いられていたが、提案型ではアナログデジタル変換器(ADC)を用いることにより、非常に良好なジッタ特性の実現が可能 (クリックで拡大) 出典:東京工業大学

デジタルPLLの校正。デジタル型位相同期回路(PLL)において、従来は時間デジタル変換器(TDC)が用いられていたが、提案型ではアナログデジタル変換器(ADC)を用いることにより、非常に良好なジッタ特性の実現が可能 (クリックで拡大) 出典:東京工業大学TDCを用いた従来の時間軸処理に対する、A-Dコンバータを用いた新方式の電圧軸処理の利点は次の通り。

- 容量により電圧値をサンプリングできる

- 正確に線形な電圧増幅ができる

- ジッタを減らすのに、余分な電力が不要

- ばらつきや電源電圧・温度変化などにより基準電圧範囲が変動しない

- 抵抗ラダー(抵抗をはしご形に接続した回路)などにより容易に中間の電圧値を生成できる

| 従来技術 TDCを用いた時間差→デジタル変換 |

新技術 ADCを用いた電圧差→デジタル変換 |

|

|---|---|---|

| 線形性 | 低い | 非常に高い |

| 分解能 | 普通 | 高い |

| ジッタ | 内部ジッタを抑えるために大電力が必要 | 低い |

| 東京工業大学の発表資料より作成 | ||

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- TSMCがGaNファウンドリー事業から撤退へ、NavitasはPSMCと提携で対応

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

- 25年5月の世界半導体市場は全地域で成長、19.8%増の590億ドルに

- 危うい再建計画 Wolfspeed、CHIPS法補助金で再生図るか

- 半導体製造ラインの立ち上げ迅速に、日本IBMが京都に開発拠点

- Qualcommの狙いは何なのか、やたらと「高い」Alphawave買収額

- 「DRAM生産の4割を米国で」 Micronを待ち受ける過酷な競争

- 22nmプロセス採用でMRAM内蔵、ルネサスがエッジAI特化の新マイコン