EE Times Japan >

プロセス技術 >

ARMから見た7nm CMOS時代のCPU設計(5)〜スタンダードセルの「スタンダード」とは何か:福田昭のデバイス通信(16)(2/2 ページ)

» 2015年03月27日 09時45分 公開

[福田昭,EE Times Japan]

高さの異なるセルを使い分ける

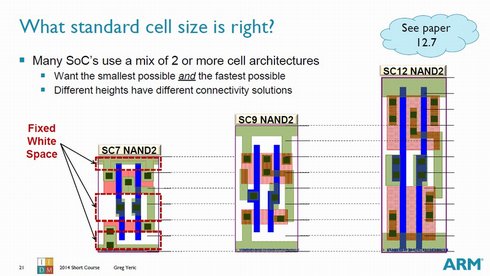

スタンダードセル方式による回路設計では、セルの高さの異なるセルライブラリをあらかじめ用意しておく。SC9のセルライブラリ、SC7のセルライブラリ、SC12のセルライブラリ、といった具合になる。一般的には、低いセルは集積密度が高く、高いセルは電流駆動能力が高い。ただし実際のレイアウトには柔軟性があるので、同じ高さでも集積密度を追求したセルと、消費電力の低さを追求したセルの両方が十分にあり得る。

SoCのレイアウト設計では、高さの違う2種類以上のセルライブラリを使い分けることが多い。例えば、低消費電力を要求する回路ブロックにはSC7のライブラリ、高速性を要求する回路ブロックにはSC12のライブラリといった割り当てをする。

同じ高さのセルで電流駆動能力を高める方法

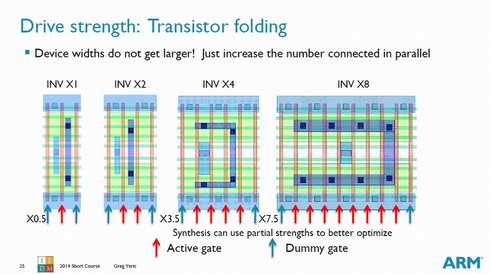

同じ高さのセルでも、電流駆動能力を高めることは可能である。最も単純な方法は、ゲート電極の本数を増やすことだ。例えばインバータでは、ゲート電極を1本から、2本、4本、8本と増やすことで、ゲート幅が実効的に広がったことになり、電流駆動能力が増加する。

ただし、ゲート電極の本数を増やすとセルの横幅が大きく伸びる。シリコンの面積が大きく増加し、製造コストの上昇を招く。低いセルを採用したことで多数本のゲート電極を使用するセルの比率が大きくなるときは、最初から高さのあるセルを採用した方が、シリコンの面積は小さくて済む。

セルの電流駆動能力を高めるために、ゲート電極の本数を増やす。SC10のCMOSインバータのレイアウト例。左端が最小単位で、ゲート電極(赤色の直線)は1本しかない。右端では8本のゲート電極を接続して1個のインバータを構成している(クリックで拡大) 出典:ARM

セルの電流駆動能力を高めるために、ゲート電極の本数を増やす。SC10のCMOSインバータのレイアウト例。左端が最小単位で、ゲート電極(赤色の直線)は1本しかない。右端では8本のゲート電極を接続して1個のインバータを構成している(クリックで拡大) 出典:ARM(次回に続く)

関連記事

「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

ルネサス エレクトロニクスは、16nm FinFETプロセスを用いてSRAMを試作したと発表した。プレーナ型MOSFETを使う場合に比べて低い動作電圧で高速読み出しに成功しているが、一方でFinFETと、微細化プロセスを用いたことによる課題も増えている。 All Programmableデバイス向け開発環境、C/C++でFPGA回路設計も可能に

All Programmableデバイス向け開発環境、C/C++でFPGA回路設計も可能に

ザイリンクスは、All Programmable SoCおよびMPSoC向けの開発環境「SDSoC」を発表した。SDSoCを用いると、FPGAを設計した経験がほとんどない技術者でも、高速化したいC/C++関数を指定するだけで、自動的にハードウェア回路に置き換えることができる。 第1回 楽しいアナログ回路設計

第1回 楽しいアナログ回路設計

「アナログ」という言葉を聞くと「古い」、「時代遅れ」、「頑固親父」なんていう印象を持つ人が多いかもしれません。アナログは「アナクロニズム(時代錯誤)」と語感が似ていることが原因かもしれませんが、アナログ回路の世界は楽しいものなのです。 第9回 発振回路を評価する3つの作業〜発振余裕度と励振レベル〜

第9回 発振回路を評価する3つの作業〜発振余裕度と励振レベル〜

今回は、前回紹介した周波数マッチング(発振周波数精度)の評価に続いて、発振余裕度(負性抵抗)と励振レベル(ドライブレベル)の評価に移りましょう。 データ変換器編:回路技術で急激に力を付ける韓国勢

データ変換器編:回路技術で急激に力を付ける韓国勢

今回は、A-D変換器、D-A変換器などのデータ変換器を扱う注目講演を紹介する。この分野では、韓国勢の台頭が目立つ。発表件数は、米国、オランダに次ぐ3位だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速