新世代SHARCはCortex-A5搭載でマイコン要らず――産業機器/車載機器市場への展開を狙う:デバイス DSP(1/2 ページ)

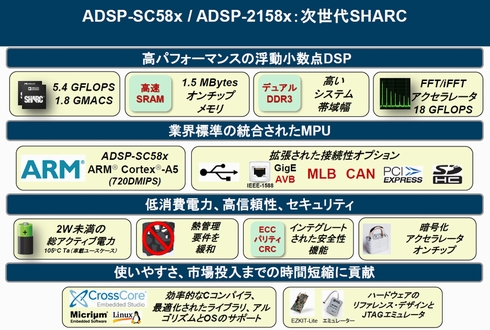

アナログ・デバイセズは2015年6月、浮動小数点DSPコア「SHARC」を搭載する新世代プロセッサとして、CPUコア「ARM Cortex-A5コア」を混載した「ADSP-SC58x」を発表した。DSPコアの性能向上などにより、電力効率が高まった他、CPUコア搭載により、インタフェース制御用マイコンを省略できる。

マイコンのコプロセッサではなく、1チップで――。

アナログ・デバイセズは2015年6月17日、浮動小数点DSPコア「SHARC」を搭載する新世代プロセッサとして、CPUコア「ARM Cortex-A5コア」を混載した「ADSP-SC58x」を発表した。Cortex-A5コアの搭載により、SHARCプロセッサと組み合わせて使用することの多かったと、マイコンが不要になり、基板サイズや消費電力削減に貢献する。

ワンチップで制御も信号処理も

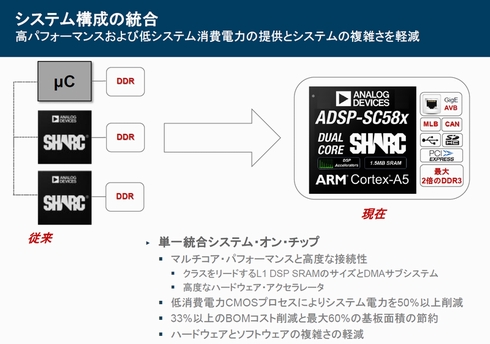

新世代のSHARCプロセッサは、新たに開発したDSPコア「SHARC+」を2個搭載するデュアルコア構成を採用した。さらに、イーサネットやPCI Express(PCIe)といった高速インタフェースなどの制御を行うためCPUコア(Cortex-A5コア)を搭載した。SHARCプロセッサが、CPUコアを内蔵したのは今回が初めてだ。

これまでのSHARCプロセッサは、浮動小数点DSPとして、高度な信号処理を担ってきた。ただ、その一方で、各種インタフェース部の制御は、マイコンで行わなければならず、SHARCを使用する場合はマイコンとの2チップ以上の構成となった。

新世代品は、これを1チップ構成で実現するプロセッサとして開発。さらに、FPGAでDSP機能やインタフェース制御機能を実現していた用途でも、SHARCプロセッサ1つで代替することを狙った。

マイコンの代わりを果たすCPUコアは、「性能、サイズ、コストのバランスを考慮し、Cortex-A5コアを選択した」(同社)。Cortex-A5コアは、一般的なマイコンに搭載されるARM Cortex-Mシリーズや同-Rシリーズよりも高性能であり、インタフェース関連制御以外にも、さまざまな制御や信号処理を実施できる能力を持つ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

- 25年5月の世界半導体市場は全地域で成長、19.8%増の590億ドルに

- 危うい再建計画 Wolfspeed、CHIPS法補助金で再生図るか

- Qualcommの狙いは何なのか、やたらと「高い」Alphawave買収額

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- 半導体製造ラインの立ち上げ迅速に、日本IBMが京都に開発拠点

- 22nmプロセス採用でMRAM内蔵、ルネサスがエッジAI特化の新マイコン

- データセンター向けAI半導体のEsperantoが事業縮小、技術売却を模索

- パワー半導体受託生産のJSファンダリが破産申請、負債総額約161億円