プレーナ型NANDフラッシュの微細化の限界:メモリ各社の製品から探る(4/4 ページ)

制御ゲート/浮遊ゲート

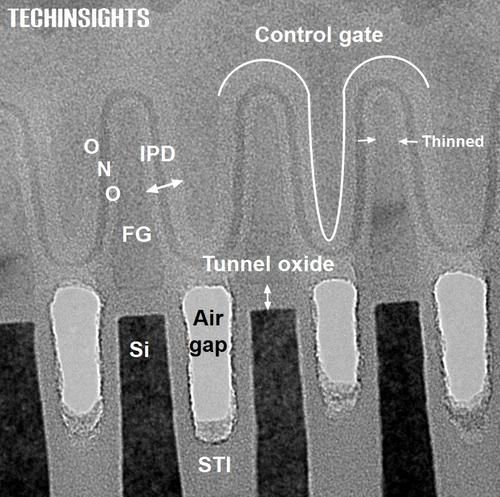

次の設計的な課題は、コントロールゲート(制御ゲート)とフローティングゲート間の高い容量結合比を保持しながら、隣接するセル間の容量結合比を軽減することである。従来、コントロールゲートは、図5に見られるように、フローティングゲートの3面を覆っている(ラップ型)。

コントロールゲートとフローティングゲート間の容量結合比は、共重合体誘電体(IPD:InterPoly Dielectric)によって与えられる。IPDは、電流とhigh-k絶縁膜に対して優れたブロッキング特性を持っていなければならない。

図5では、酸化物/窒化物/酸化物(ONO)層が確認できる。IPDがかなり厚いため、隣接するフローティングゲートの間のコントロールゲートのギャップを軽減できる。SK-Hynixは、フローティングゲートの側面を薄くして、コントロールゲートの幅を広げた。TechInsightsは、SK-Hynixが、シリコンチャネル間にエアギャップ(Air gap)を加え、容量結合比を低減している点に注目している。

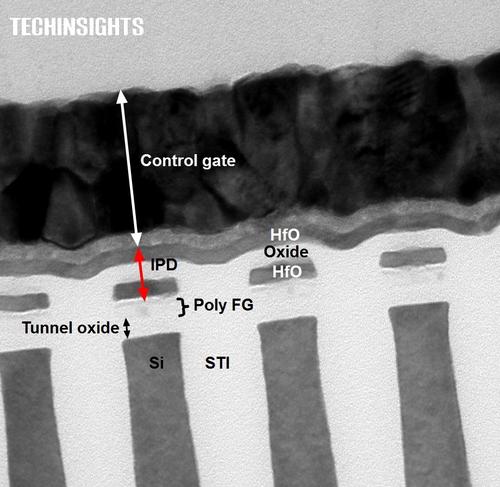

図6は、Micronの16nm NANDフラッシュのコントロールゲートおよびフローティングゲートの構造だ。Micronは、プレーナ型のコントロールゲート・フローティングゲートを使う方が好みのようである。Micronはポリシリコンのフローティングゲートを採用し続けているが、その厚みは現在、相当薄くなっている。薄くなったことで、HfO2(酸化ハフニウム)などのIPD層が、フローティングゲートの上に、ほぼ平らに構築できている。

プレーナ型NANDメモリでは、リソグラフィ技術による微細化は限界が来ているようにみえる。クアッドパターニングを適用した液浸リソグラフィは、1Xnm世代の後半までしか使えないだろうし、エアギャップは、セル間の干渉を抑えるために既に広く採用されている。Samsung、SK-Hynix、東芝が採用しているラップ型は10nmまで、Micronのプレーナ型フローティングゲートはサブ10nmまでの微細化が限度だと思われる。最終的には、NANDフラッシュは3次元の方向に進むだろう。

【翻訳:滝本麻貴、田中留美、編集:EE Times Japan】

関連記事

2019年までのストレージ市場を展望する(前編)

2019年までのストレージ市場を展望する(前編)

米国のストレージ専門調査会社TRENDFOCUSは、2015年5月に東京で開催された「DiskCon Japan 2015」で、ストレージ市場の最新状況を解説するとともに、2019年までの市場動向を展望した。今回は、ハードディスク装置(HDD)の市場動向に関する講演内容を紹介する。 ムーアの法則、その行方を聞く

ムーアの法則、その行方を聞く

これまで何度となく“終えん説”が唱えられてきたムーアの法則だが、半導体業界は多大な労力でこの法則を維持している。今後、ムーアの法則はどうなっていくのか。業界のキーマンに、ムーアの法則の行方や、ムーアの法則の維持に関わる技術などについて話を聞いた。 ムーアの法則、50年をたどる

ムーアの法則、50年をたどる

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。 FinFET以降の半導体製造技術はどう進む? IBMの見解

FinFET以降の半導体製造技術はどう進む? IBMの見解

「Common Platform Technology Forum」において、IBMが半導体製造技術の将来展望について発表を行った。液浸リソグラフィによるダブルパターニング技術やFD-SOI技術に加え、カーボンナノチューブ、シリコンフォトニクス、ナノワイヤーなどのキーワードを交えて半導体製造の将来像や課題などが示された。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

図5 16nm NANDフラッシュのコントロールゲート TechInsights

図5 16nm NANDフラッシュのコントロールゲート TechInsights 図6 Micronの16nm NANDフラッシュ

図6 Micronの16nm NANDフラッシュ