EE Times Japan >

プロセス技術 >

抵抗変化メモリとGaNデバイス:福田昭のデバイス通信 IEDM 2015プレビュー(4)(2/3 ページ)

» 2015年11月10日 09時30分 公開

[福田昭,EE Times Japan]

InGaAs FETとSiGe FETをモノリシック積層したCMOS回路

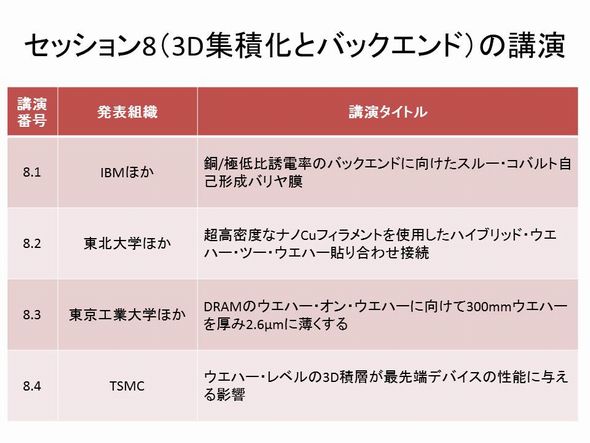

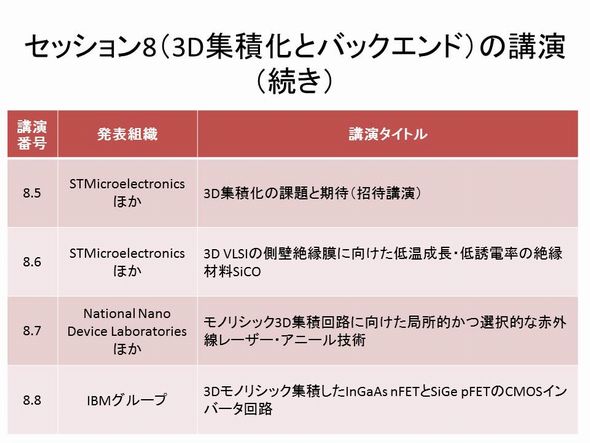

セッション8(プロセス技術と製造技術)のテーマは「3D集積化とバックエンド」である。かつては3次元(3D)集積回路の製造技術ではウエハーの貼り合わせが主流だった。今回は、ウエハー貼り合わせ技術に加え、モノリシックに3次元(3D)の集積回路を実現しようとする試みが目立つ。

東北大学とXilinxの共同研究グループは、Cuフィラメントと異方性導電フィルムを利用した高密度かつ多ピンのウエハー貼り合わせ技術を報告する(講演番号8.2)。熱圧着のウエハー貼り合わせによって直径3μmのCu電極を13万6800本、形成した。

東京工業大学とディスコの共同研究チームは、2Gビット DRAMを形成した300mmウエハーを2.6μmまで薄くする技術を開発した(講演番号8.3)。ウエハーを薄くしていったときに、厚みが5.6μmまではDRAMの電荷保持特性で劣化はまったく見られなかった。厚みが2.6μmのときは、電荷保持特性が劣化した。

ドイツのIBM Researchと米国のIBM T.J. Watson Research Centerは、絶縁基板の上にInGaAs nチャンネルFETとSiGe pチャンネルFETをモノリシック積層した3次元のCMOS回路を製造した結果を共同で発表する(講演番号8.8)。トップ層がInGaAs、ボトム層がSiGeである。トップ層の形成によってボトム層のトランジスタ性能は劣化していない。CMOSインバータを試作して電源電圧0.25Vで動作を確認した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速