ルネサス「世界最速/高集積」の画像処理用SRAM:16nm世代の自動運転車向けSoCに展開へ(2/3 ページ)

2種のクロックを生成する回路とアドレスラッチ回路を改良

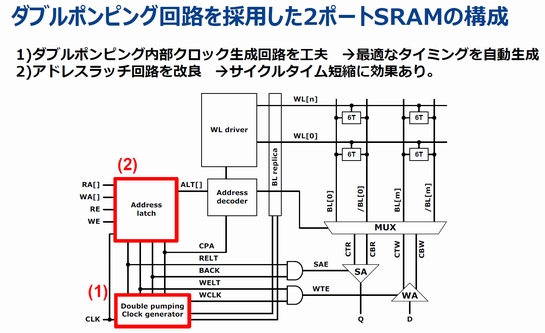

高速2ポートSRAMの実現のため、ルネサスは新たに2つの新規技術を開発した。

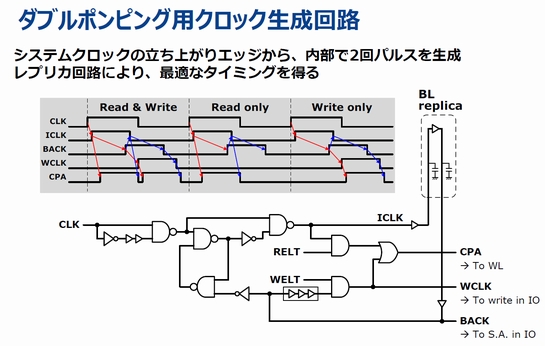

1つは、通常のクロックを基に、読み出し用クロックと書き込み用クロックの2種類のクロックを1クロックサイクル内で生成するための「ダブルポンピング回路技術」だ。通常のクロック信号を二手に分け、一方の信号は、そのまま読み出し用クロックとして使用する。もう一方の信号は読み出し後に行う書き込み用クロックとし、レプリカ回路という遅延回路を通し、通常のクロック信号(=読み出しクロック信号)とタイミングを遅らせてから、メモリセルへ出力する。これにより、1クロックサイクル内で2回のクロックを生成することが可能になった。なお、レプリカ回路は、遅延させる時間を自動的に最適化できるようにし、「調整の手間なども必要ないようになっている」とする。

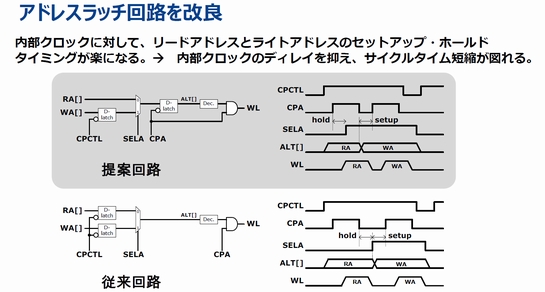

ダブルポンピング回路により1サイクルで2回のクロックを生成できるようになったが、読み出し用クロックと書き込み用クロックの切り替わり時間は短時間であるため、切り替わり時に行う読み出しアドレス/書き込みアドレスのホールド/セットアップの時間的余裕が乏しくなる。そこで、アドレスラッチ回路を改良し、ホールド/セットアップを行うタイミングを変更し、時間的余裕を持たせ、短いサイクルタイムでも安定してホールド/セットアップを行えるようにした。

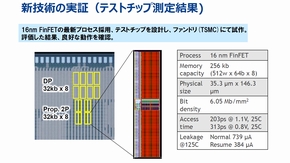

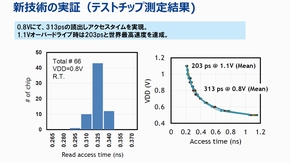

ダブルポンピング回路技術と改良版アドレスラッチ回路技術の2つの新技術を適用し、6Tr構成の2ポートSRAMを16nm FinFETプロセスで試作評価したところ、0.8Vの低電圧動作時で読み出し時間313psでの高速安定動作を確認した。この読み出し速度は、2015年にルネサスが開発、発表した16nm FinFETプロセス向けデュアルポートSRAMと「ほぼ同等の速度」とする。さらに、動作電圧1.1Vのオーバードライブ時には203psを記録。「この値は、世界最高速度」(ルネサス)とする。

面積当たりの容量は、同デュアルポートSRAMより1.8倍大きい6.05Mビット/mm2で、「世界最高の集積度も同時に実現した」とする。リーク電流も、同一容量で従来のデュアルポートSRAMと比較して、素子数が減り、チップサイズが縮小したことで半減した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化