「SEMICON West 2016」、imecが展望する5nm世代の配線技術(前編):福田昭のデバイス通信(94)(1/2 ページ)

imceによる、5nm世代のロジック配線プロセスを展望した講演を、前後編の2回にわたりお届けする。前半では、配線抵抗(R)、配線容量(C)、RC積という配線のパラメータの特徴を紹介する。さらに、10nm世代、7nm世代、5nm世代と微細化が進むと、配線抵抗(R)、配線容量(C)、RC積がどのように変化していくかを解説する。

回路性能に影響する配線パラメータの違い

半導体製造装置と半導体製造用材料に関する北米最大の展示会「SEMICON West 2016」が7月12日〜14日に米国カリフォルニア州サンフランシスコのモスコーンセンター(Moscone Center)で開催された。12〜14日には「FORUM」(フォーラム)と称する併設の講演会があり、専門テーマに関する解説や展望などを数多くの研究者や技術者、経営者などが発表した。

今回は、次世代のプロセス技術を展望するフォーラムについてご紹介したい。14日の午前には、配線技術の将来に関するフォーラム「Interconnect Solutions for Next Generation Computers」が開催された。その中で、ベルギーの研究開発機関imecによる5nm世代のロジック配線プロセスを展望した講演が参考になったので、前後編の2回で概要をご紹介したい。講演タイトルは「Interconnect Technology Challenges and Future Direction」、講演者はimecでPrinciple Member of Technical Staff and BEOL Integration Managerを務めるChristopher J. Wilson氏である。

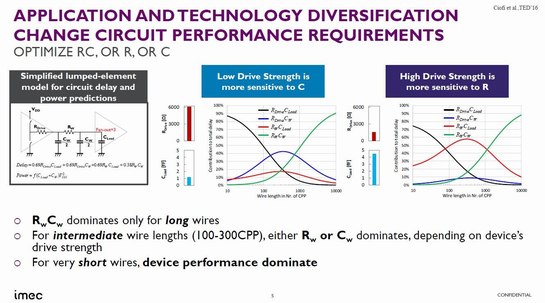

現在のロジック半導体は、IoT(Internet of Things)、モバイル、サーバといった用途に応じて回路技術やデバイス技術、プロセス技術を最適化するようになっている。配線技術も変わらない。配線のパラメータはいくつか存在しており、その中で抵抗(R)と容量(C)の積を重視するか、抵抗(R)を重視するか、容量(C)を重視するかは、回路によって違う。具体的には、トランジスタのスイッチング特性や負荷の大きさ、配線の長短などによって重視するパラメータが異なってくる。

例えばRC積が回路の性能を大きく左右するのは、配線が非常に長い場合に限定される。一方で、配線がある程度の長さ(100CPP〜300CPP、CPP: Contacted Poly Pitch)の場合は、ドライバの強さがRとCのどちらに影響されやすいかを決める。ドライバが弱いときは容量Cの影響を受けやすく、ドライバが強いときは抵抗Rの影響を受けやすい。そして配線が極めて短いときは、回路の性能はトランジスタの性能によって主に決まる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- Intelの最新AI戦略と製品 「AIが全てのタスクを引き継ぐ時代へ」

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ