NVIDIAが高性能コンピュータの回路技術を解説:福田昭のデバイス通信(96) 高性能コンピューティングの相互接続技術(1)(1/2 ページ)

2016年12月に米国サンフランシスコで開催された「IEDM2016」。そのショートコースから、NVIDIAの講演を複数回にわたり紹介する。初回となる今回は、コンピュータ・システムにおいてデータのやりとりに消費されるエネルギーをなぜ最小化する必要があるのか、その理由を28nm CMOSプロセスで製造したSoCを用いて説明しよう。

相互接続(インターコネクト)に関する課題に焦点

半導体デバイス技術に関する国際会議「IEDM」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。2016年12月のIEDM2016では、「コンピュータを実現する設計と製造(Design and Technology Enablers for Computing Applications)」と題したショートコースが開催され、1日間で6つの講義が実施された。

その中から、「将来のコンピュータにおける相互接続の課題(Interconnect Challenges for Future Computing)」と題するNVIDIAの講義が興味深かったので、今回からシリーズとして講義の概要をお届けする。講演者はNVIDIAで研究担当シニア・バイスプレジデント兼チーフサイエンティストを務めるWilliam(Bill) Dally氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Dally氏の内容を適宜、補足している。あらかじめご了承されたい。

コンピューティングチップの性能を左右する消費電力が阻む

コンピュータ・システムにおける相互接続で設計者が望むのは、データのやりとりに要するエネルギーを最小限にすることである。具体的には、伝送距離(mm)当たりと伝送ビット数(bit)当たりのエネルギー(fJ)を最小化したい。

なぜ、エネルギーを最小化したいのだろうか。1回の演算処理が必要とするエネルギー(Ops/J)が、コンピュータの演算性能(Ops/s)を決めるからだ。そしてエネルギーの多くは、相互接続におえるデータのやりとりで消費される。

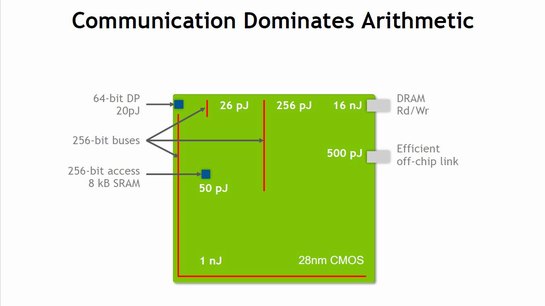

SoCシリコンダイではバスやリンクが演算器よりも大きなエネルギーを消費

このことを、28nmのCMOS技術で製造したSoC(System on a Chip)シリコンダイで具体的に説明しよう。SoCは、64ビットの倍精度浮動小数点演算器や256ビット入出力の埋め込みSRAM、長さの異なる256ビット・バス、外付けチップとのリンク、外付けDRAMとのリンクなどを搭載する。これらのユニットが演算処理によって消費するエネルギーはかなり違う。

消費するエネルギーを見ていくと、64ビットの倍精度浮動小数点演算ユニットが20pJ、埋め込みSRAMが50pJと数十pJで済むのに対し、外付けDRAMのリンクは16nJと1000倍近いエネルギーを必要とする。256ビット・バスの消費エネルギーはバスの長さによって違う。短いバスでは26pJと少ないものの、長いバスでは1nJとかなり大きくなる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- 「DRAM生産の4割を米国で」 Micronを待ち受ける過酷な競争

- 25年Q1のファウンドリー市場は縮小緩やかも、Samsung/GFは大幅低迷

- 「Switch 2」を分解 NVIDIAのプロセッサは温存されていた?

- 「やっぱりルネサスだと言われないと」 柴田CEOが原点回帰を強調

- RISC-V移行の流れ、欧州では「もう止められない」

- 300mmファブ生産能力、2nmは2028年に月産50万枚へ

- Micronの四半期業績、売上高が過去最高を更新

- SiCパワーデバイス市場は年率20%で成長、30年に103億ドル規模に

- 最大の壁、p層を克服!酸化ガリウムでFLOSFIAが達成した「世界初」